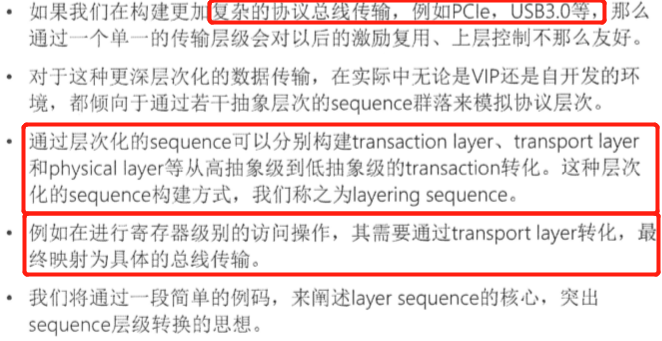

8.layering sequence

(1)概述

-

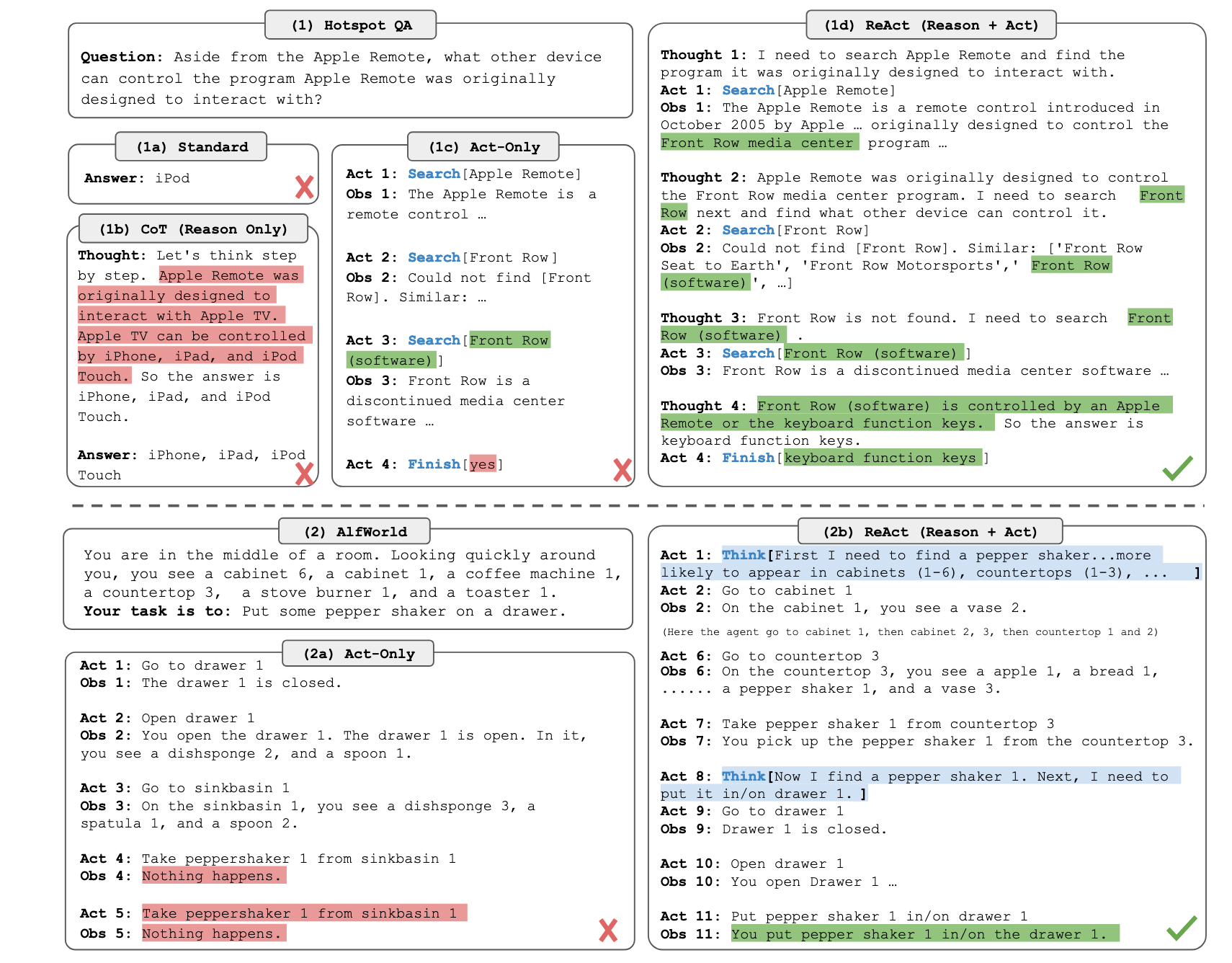

转化:高抽象级item,中间的sequence,低抽象级item。

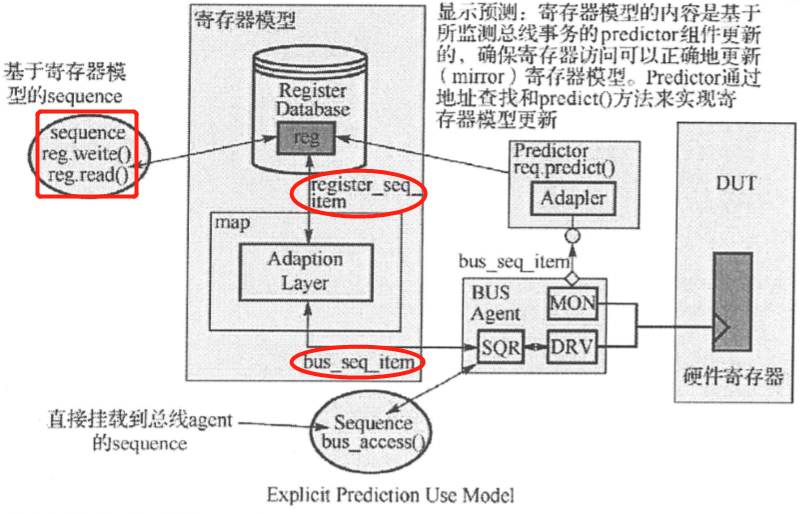

(2)寄存器模型的示意图

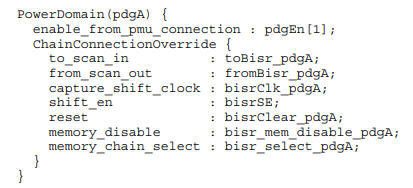

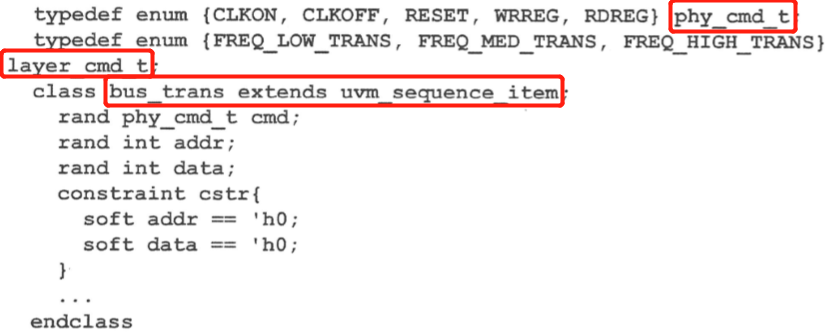

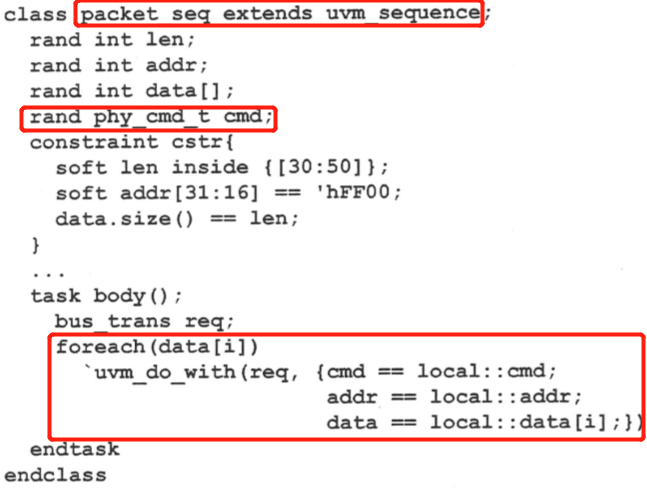

(3)示例代码:bus packet sequence

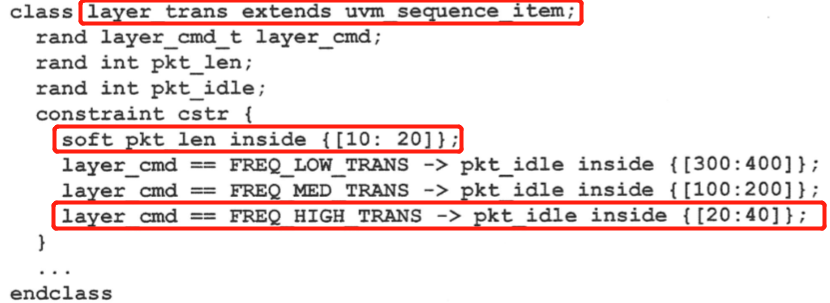

(4)示例代码:layer packet sequence

-

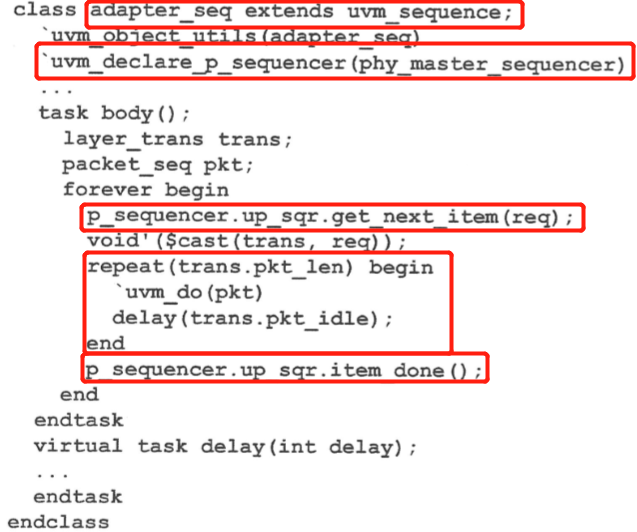

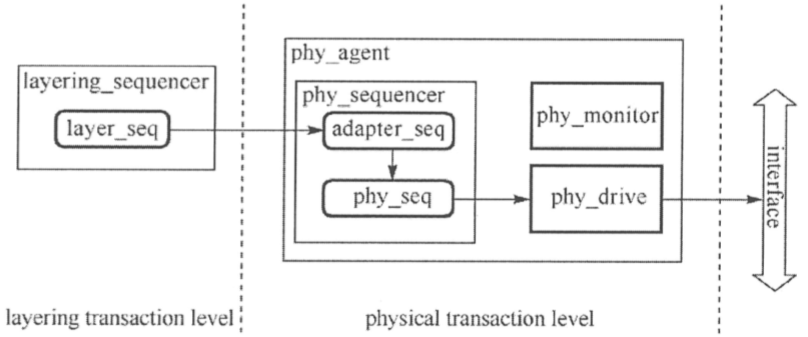

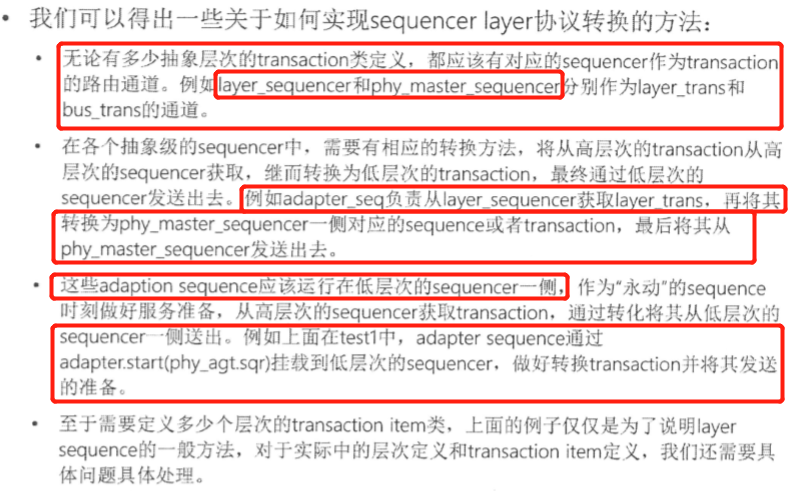

adapter_seq负责从高层次的transaction从高层次的sequence(layer_sequence)获取,继而转换为低层次的transaction,最终由低层次的sequence(physcial)发送出去。

-

adapter_seq宏声明了p_sequencer,类型为phy_master_sequencer,所以phy_master_sequencer是virtual sequencer。

-

layering_sequencer up_sqr; 从up_sqr中获得item。

-

'uvm_do(pkt):将packet_seq挂载到adapter_seq上。

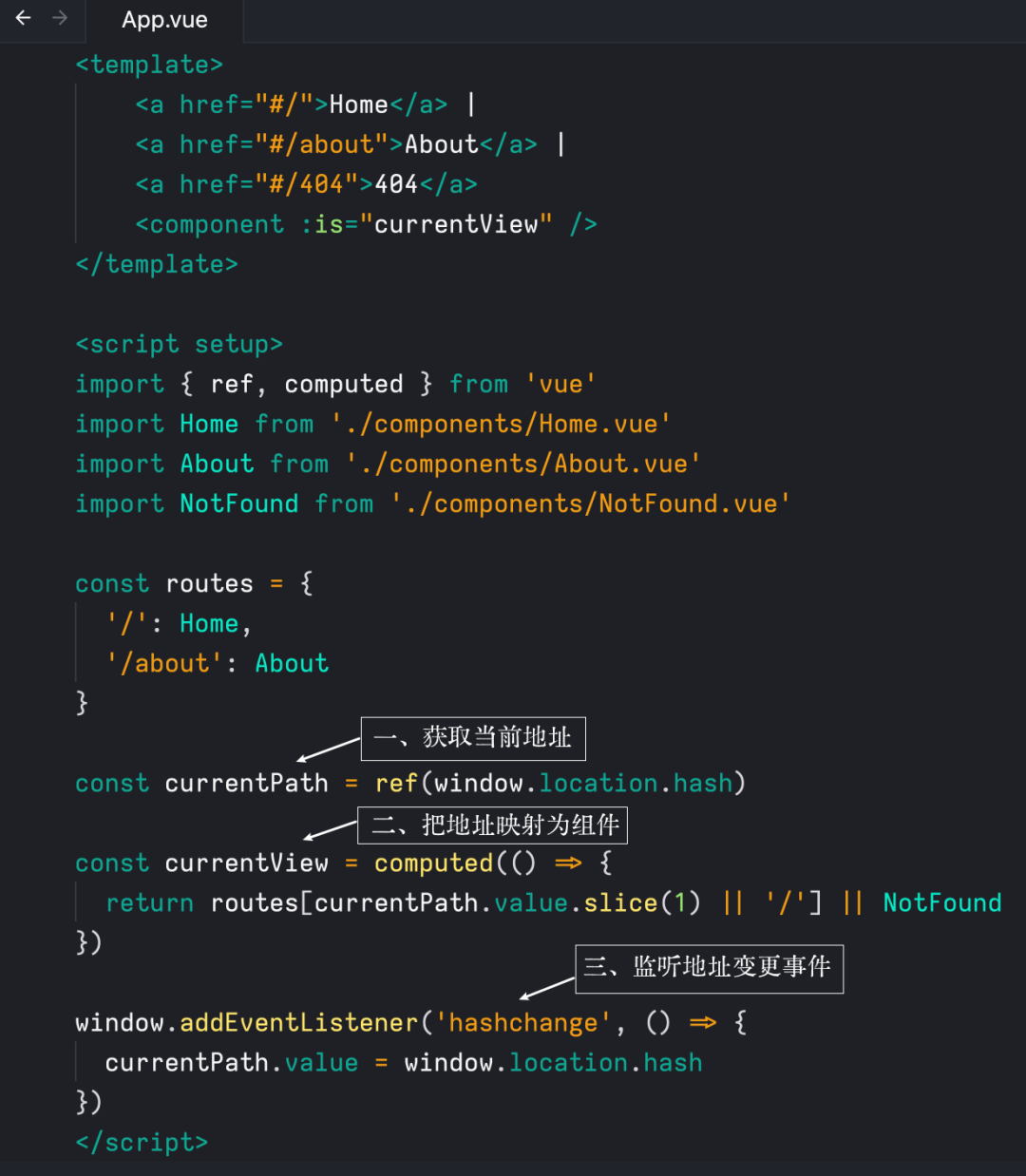

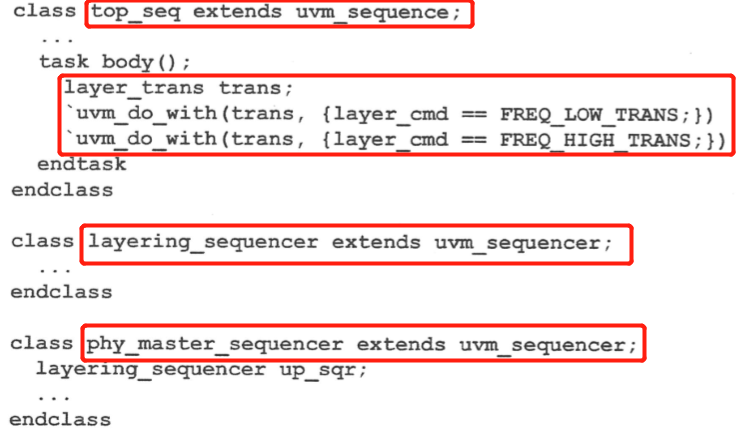

(5)示例代码:top sequence、layering_sequencer、phy_master_sequencer

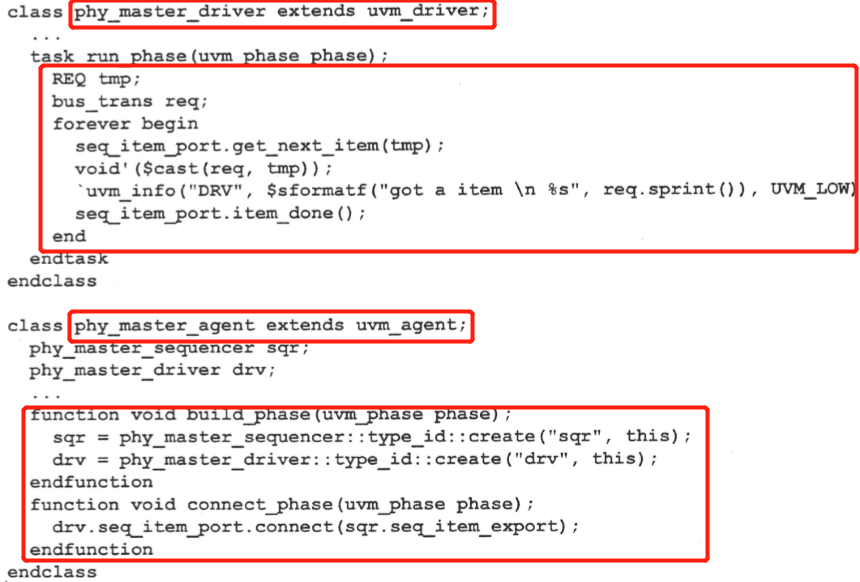

(6)示例代码:phy_master_driver、agent

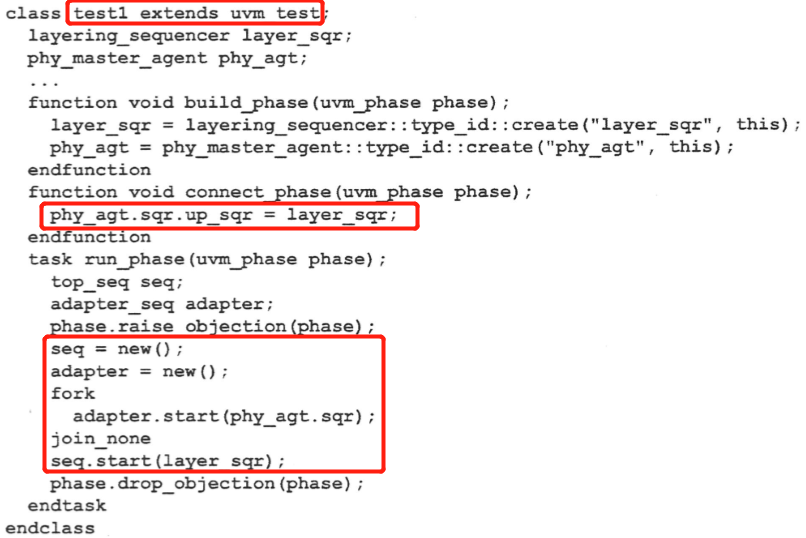

(7)示例代码:test

virtual sequence在顶层需要连接。

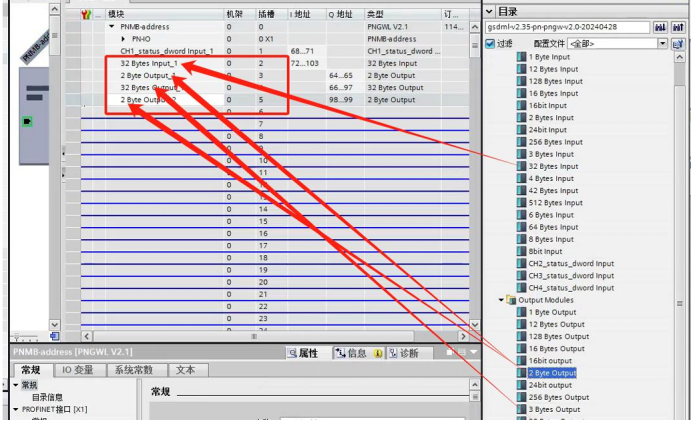

(8)图示

(9)示例解释

1.寄存器模型概述

(1)寄存器与硬件的关系

-

寄存器模型的作用:反映硬件的状态:比如mcdf中fifo的状态。

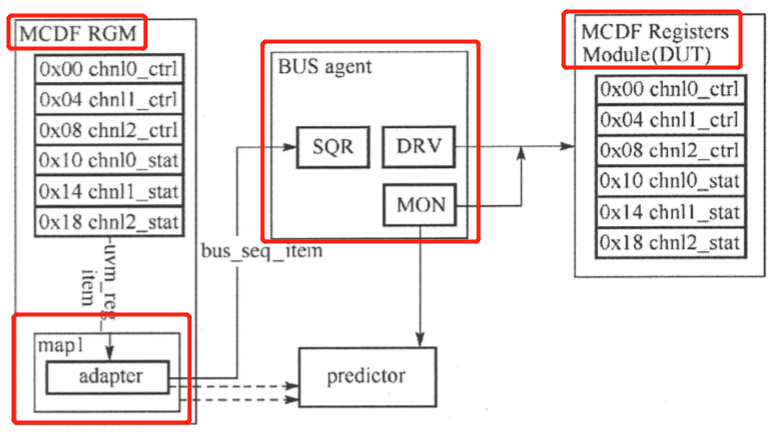

(2)寄存器模型+UVC

(3)域、属性

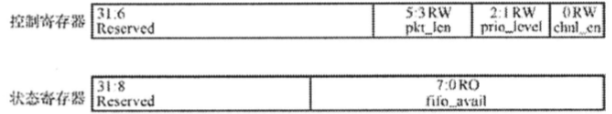

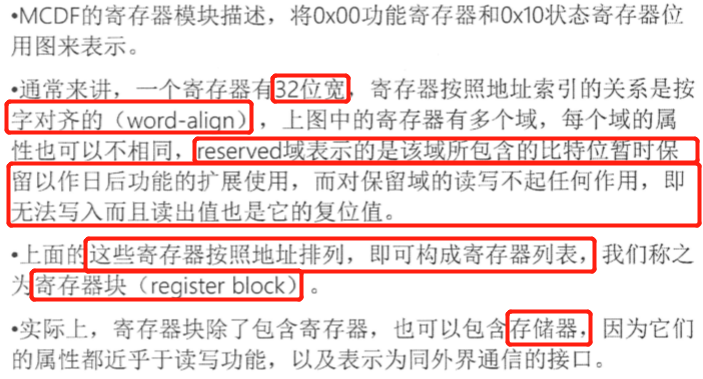

(4)寄存器块、reserved

(5)寄存器模型、总线访问寄存器的方式、寄存器模型访问的方式

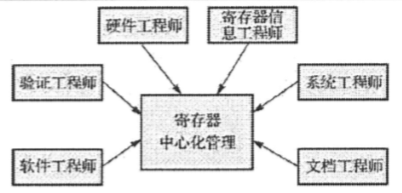

2.中心化管理方式

(1)示图

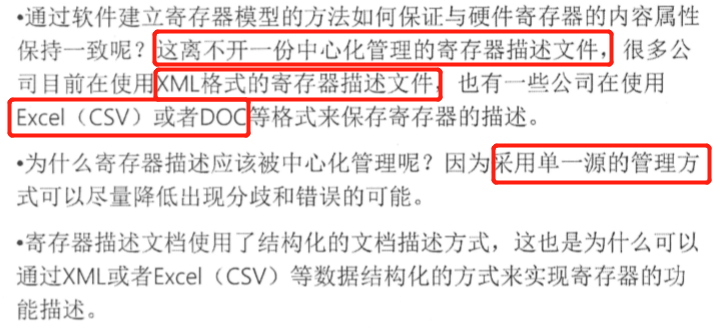

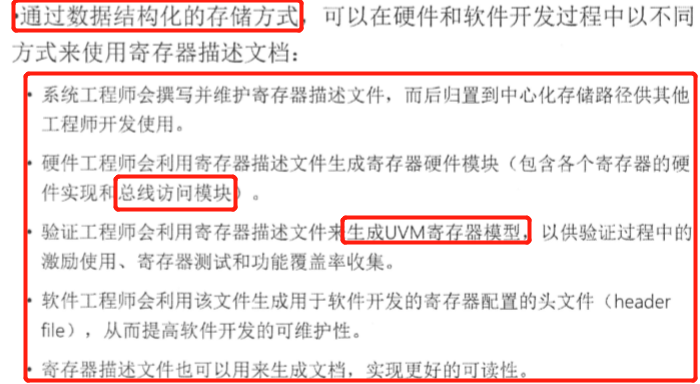

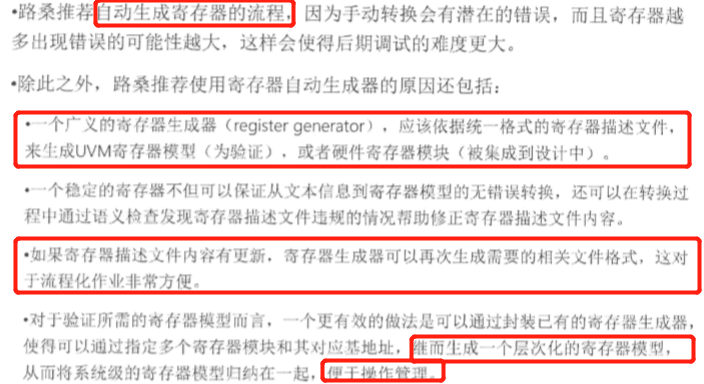

(2)

(3)

(4)

3.MCDF寄存器模型

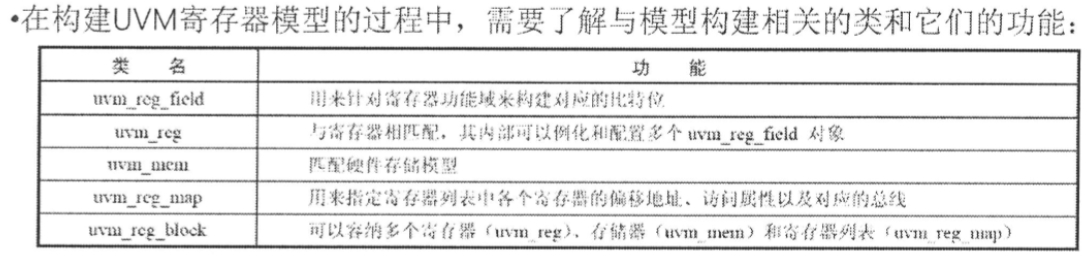

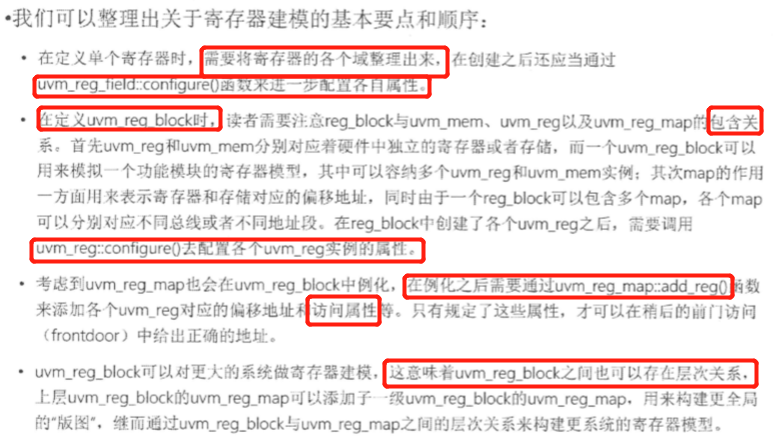

(1)uvm_reg相关概念

-

包含关系:uvm_reg_block>uvm_reg>uvm_reg_field;uvm_reg_block还包括uvm_reg_map。

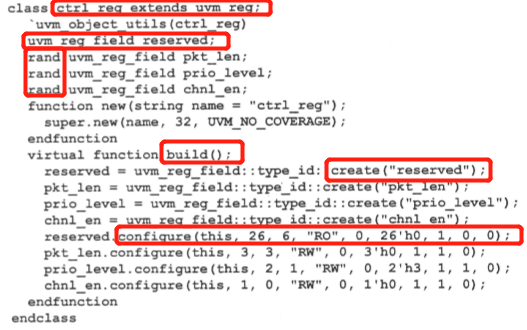

(2) 代码示例

[1]uvm_reg中new()函数中把这个寄存器的宽度作为参数传递给super.new函数:

如super.new(name, 16, UVM_NO_COVERAGE); 第1个参数是name, 第2个参数是寄存器的宽度,第3个参数是否要加入coverage。

[2]uvm_reg也是属于uvm_object类,uvm_reg_field是寄存器模型最小单位。

[3]rand的作用:设置寄存器模型期望值随机化。

[4]uvm_reg中的build类似于component中的build_phase,做创建和配置。

[5]reserved.configure(this, 26, 6, "RO", 0, 26'h0, 1, 0, 0);9个参数依次是:parent、位数(size)、起始bit位(lsb_pos)、“RO”(access)、volatile(表示是否是易失的(volatile),一般不会使用)、26‘h0:reset value、has_reset、is_rand、individually accessible(表示这个域是否可以单独存取)。

[6]uvm_reg中配置了uvm_reg_field的属性:比如RW;但是uvm_reg的属性在uvm_reg_map中配置。

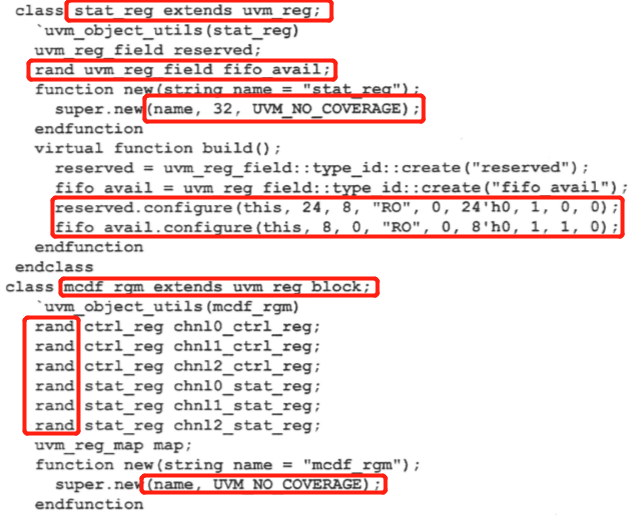

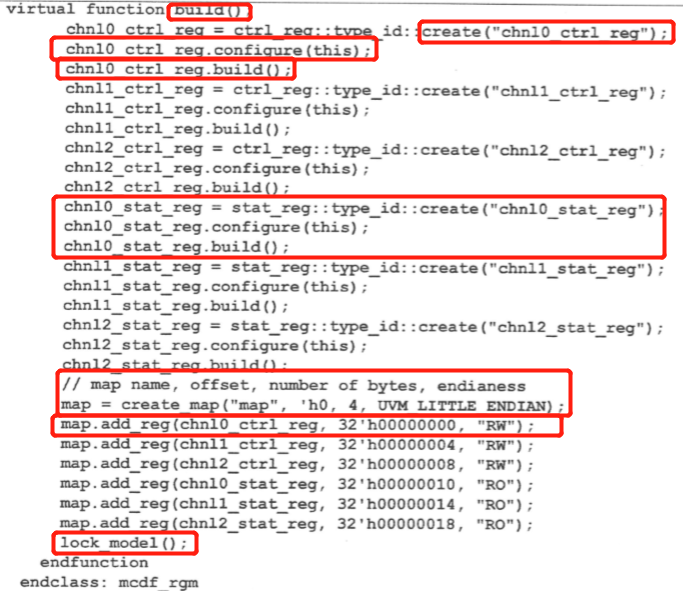

[7]在reg_block中要对reg进行create、configure、build,config是将reg和当前的block关联起来,不像之前中env中run()会自动调用其子模块的run()。

[8]在reg_block中例化uvm_map,create_map("map",'h0,4,UVM_LITTLE_ENDIAN,0):其中第一个参数是名字,第二个参数是基地址,第三个参数则是系统总线的宽度,这里的单位是byte而不是bit,第四个参数是大小端,最后一个参数表示是否能够按照byte寻址。

[9]map.add_reg():配置reg的基地址和属性。

[10]以lock_model()结尾,该函数的功能是结束地址映射关系,并且保证模型不会被其它用户修改。

(3)总结

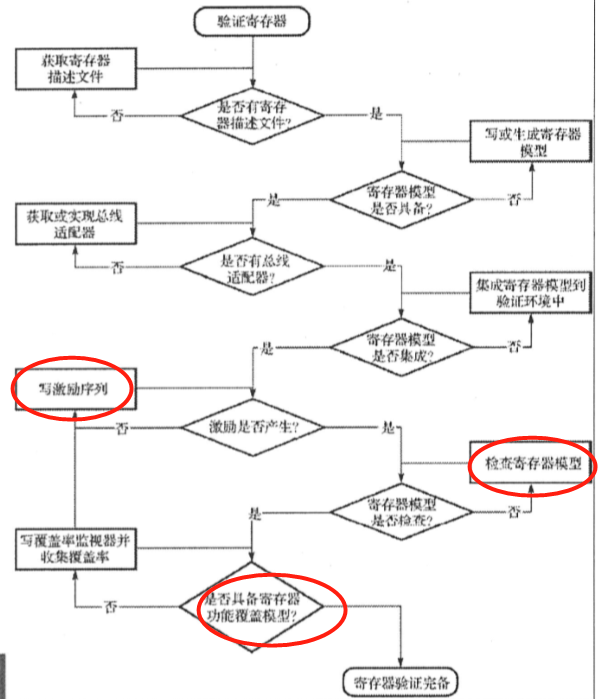

4.模型使用流程

(1)概述

(2)图示

-

寄存器模型的三个优势:

-

寄存器序列激励更好,可读与复用性更强。

-

检查硬件的寄存器模型更方便。

-

收集寄存器覆盖率。

(3)总结

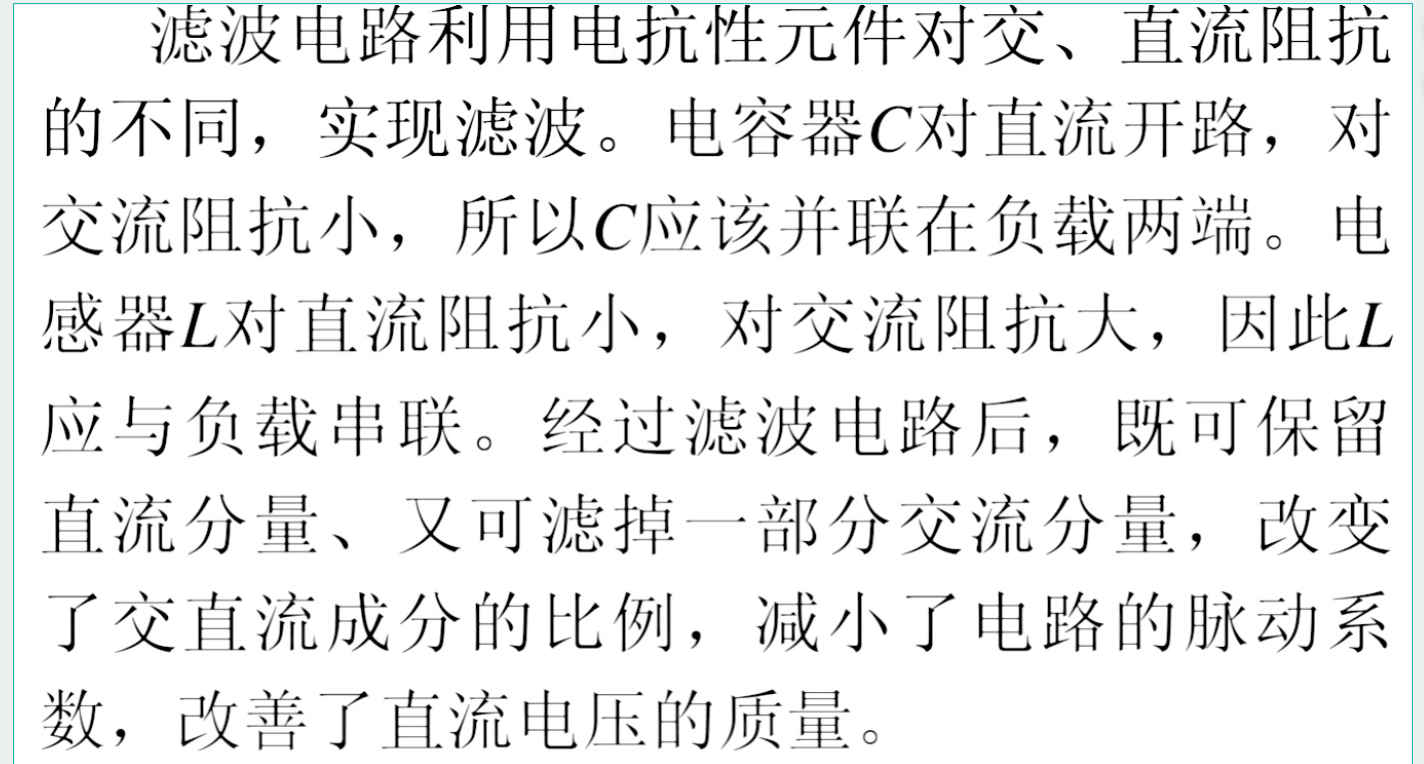

5.总线UVC的实现

(1)UVC

-

UVC的全称是UVM component,往往是构建环境中所用到的最底层的组件。

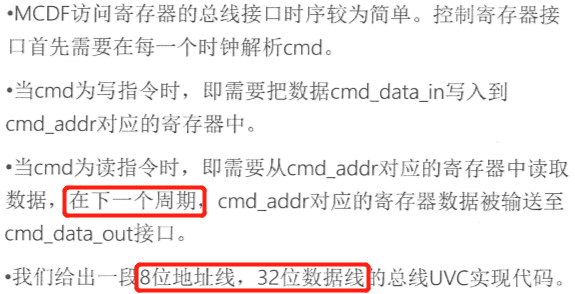

(2)MCDF访问寄存器总线接口

-

8位地址、32位数据线指的是地址有2^8个,每个地址对应的单元是32位的数据。

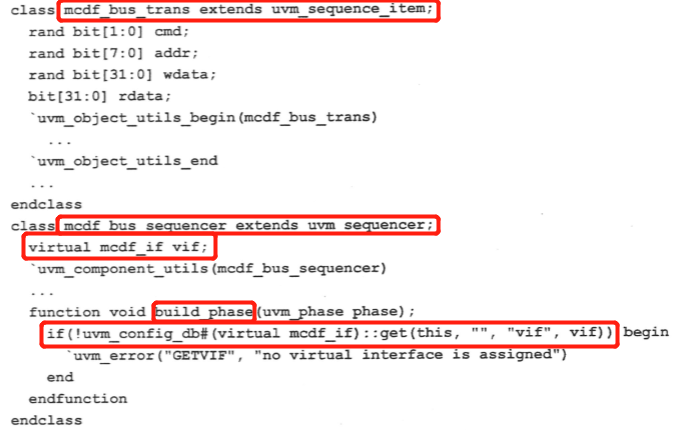

(3)MCDF访问寄存器接口的UVC代码:uvm_sequence_item、uvm_sequencer

-

在sequencer(component)中调用了mcdf_if接口;

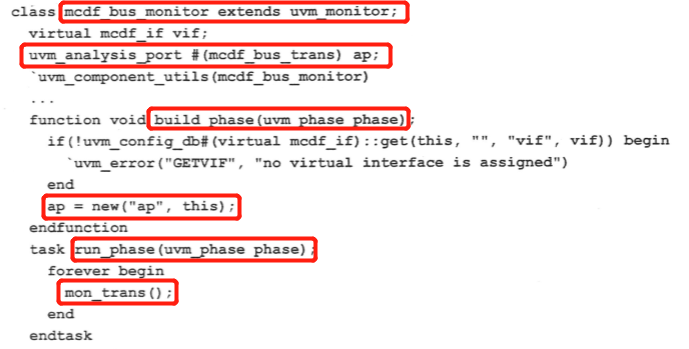

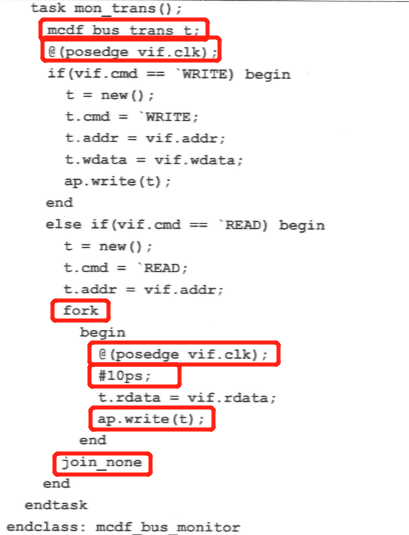

(4)MCDF访问寄存器接口的UVC代码:uvm_monitor

-

uvm_analysis_port定义了广播RSP的TLM端口,类似于driver上定义的。

-

mon_trans()做的是监测数据的传输。

-

ap.write(t):write是一个内建函数,将transaction写入ap。

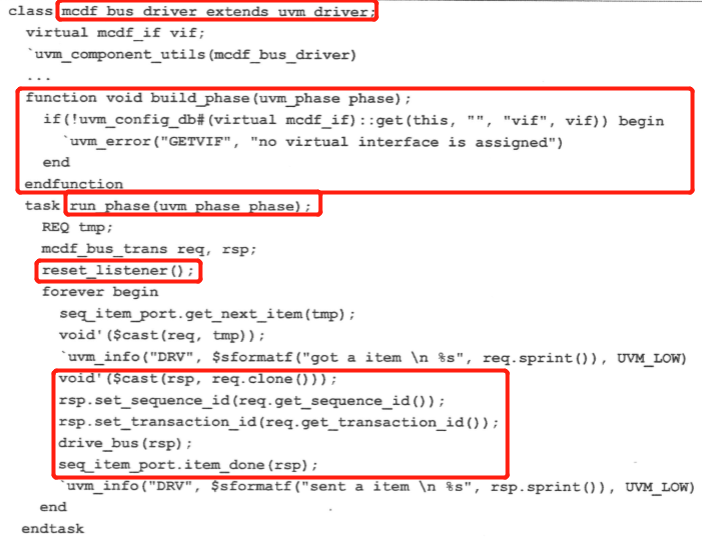

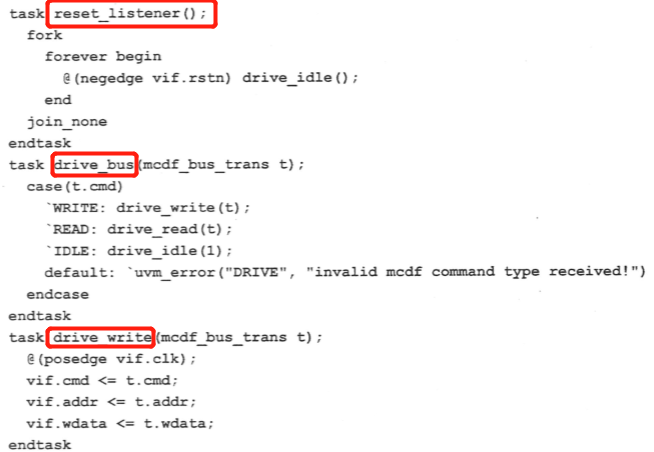

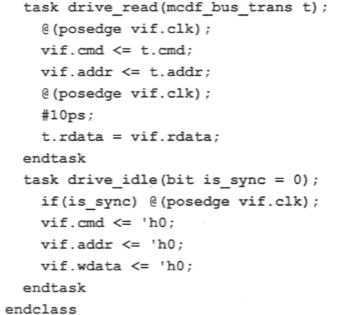

(5)MCDF访问寄存器接口的UVC代码:uvm_driver

-

get_sequence_id:根据rsp的sequence_id来找到这个rsp是哪个sequence发送的(每个req item在经sequence发送的时候够会带有unique id值);

-

get_transation_id:在sequence中调用get_response时,不指定transaction_id的话,默认是pop_front response_queue队列中的元素,同时get_response也可以指定要get确定transsaction_id的item,只需要输入相应的参数即可。比如id=req.get_transaction_id(); get_response(rsp,id);

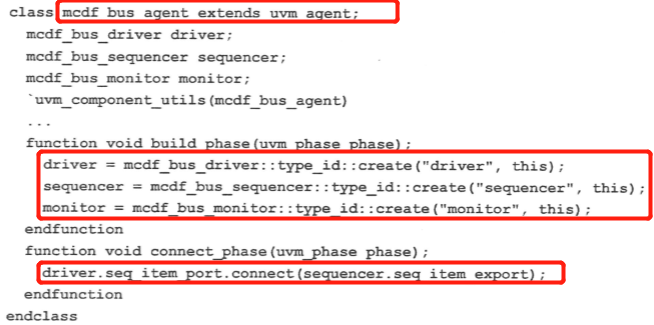

(6)MCDF访问寄存器接口的UVC代码:mcdf_bus_agent

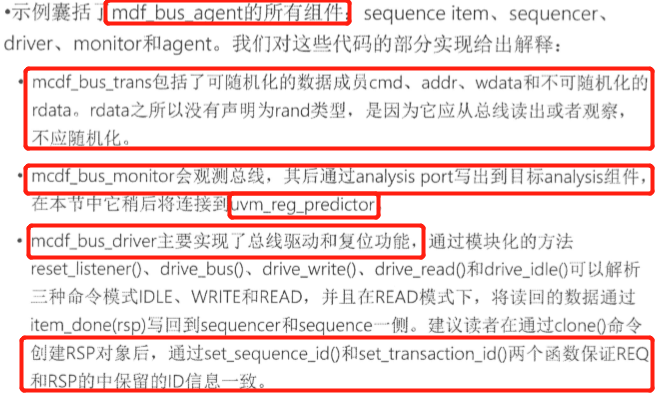

(7)示例解析

![[ctfshow web入门] web78](https://i-blog.csdnimg.cn/direct/57c4ad956db54d3681140bd799b32e02.png)