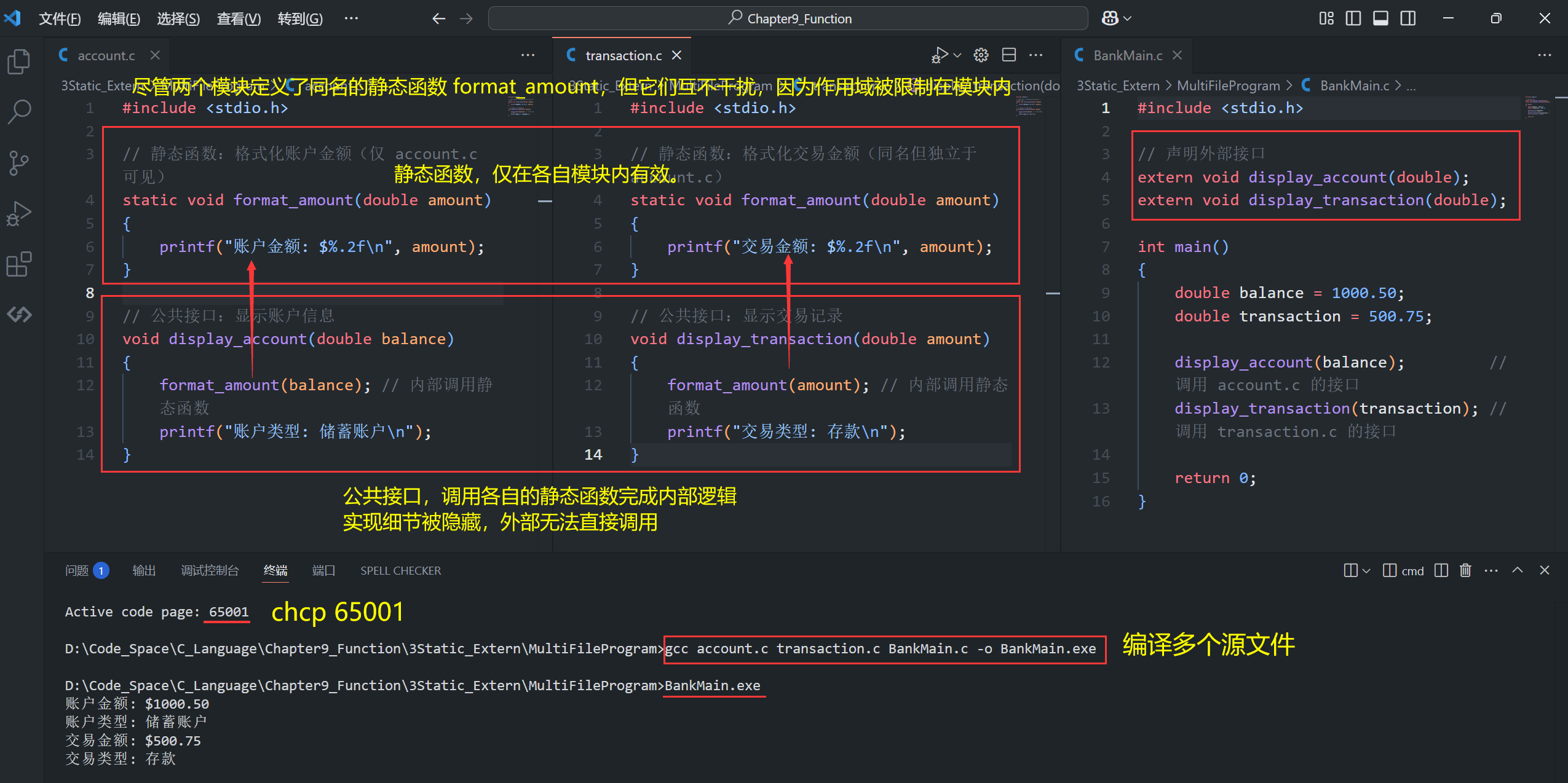

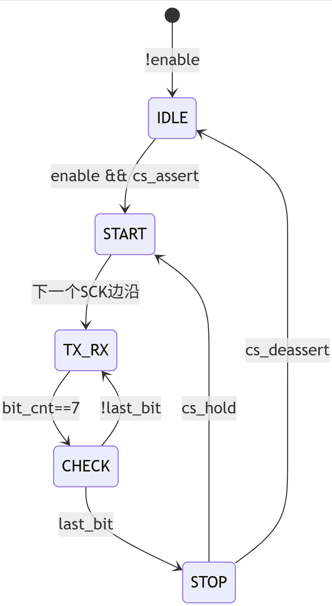

搞懂写,把下面这幅图搞定,基本上就掌握了7成了。

术语解释

WL : write latency,说的是命令到发送数据的WDQS的间隔,注意这里不包含twpre1的时间,通过配置MR1实现。

twpre1: 在发送写数据之前,WDQS第一个边沿到,写数据时刻的间隔,固定的是2。

tdqss: dqs的边沿和CK边沿之间的间隔

twdqs2dq_i: wdqs 到dq间隔

现在步入正题,分析。

发送命令后,多久才会发送数据呢? 记这个时间为T1。

则T1 = WL * tck + tdqss + tdqs2dq

发送命令后,多久才会发送wdqs? 记这个时间为T2。

则T2=(WL-1)*tck + tdqss

那么发送wdqs到发送数据的间隔呢?

T1-T2= tck + tdqs2dq

想一下这个地方为啥查了约1个tck,原因是在发送数据之前,一定要提前发送wdqs 2个周期,刚好wdqs的时钟是tck的2倍,因此约1个tck。可是这里面多了一个tdqs2dq。这样分析下来,和规格有点mismatch。如下图所示,规格中明确说了,可以通过训练的方式,让DQ的中心对其WDQS的边沿,那么这时候就没有这个tdqs2dq。那么T1=WL*tck + tdqss。

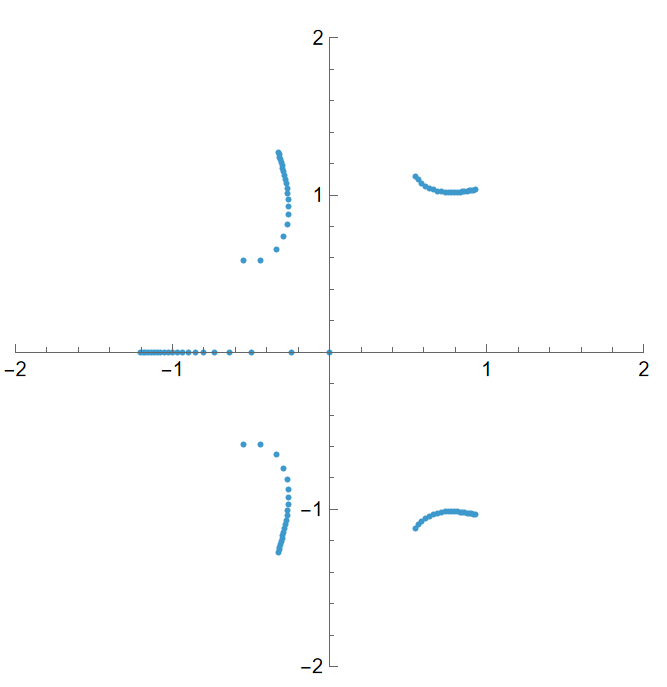

如下为,一笔写操作的波形。很明显preamble和postamble都是2个cycle。

讨论过1笔操作,我们继续讨论多笔操作。

当两笔写操作的间隔是tccd=2时候,dq可以做到无缝连接,这个时候写的效率是最高的。注意这个和两个不同的bank的写操作。由下图可知,相同的bank的操作的话,就需要更长的时间,最少是4个tck。

关于写之后读操作,写之后precharge的操作,本篇不再赘述,感兴趣的可以阅读spec,笔者不才,若有错误,请纠正。