低功耗IC(集成电路)设计是现代电子产品的关键要素,因为它可以延长电池寿命并降低设备的能耗。电池供电设备市场的不断增长,使得芯片设计人员必须认真考虑各种降低IC功耗的技术。目前有多种技术可用于降低IC的静态和动态功耗。静态功耗的来源包括直流电流和漏电流,而动态功耗则与频率相关,主要来自晶体管的开关和短路功耗。

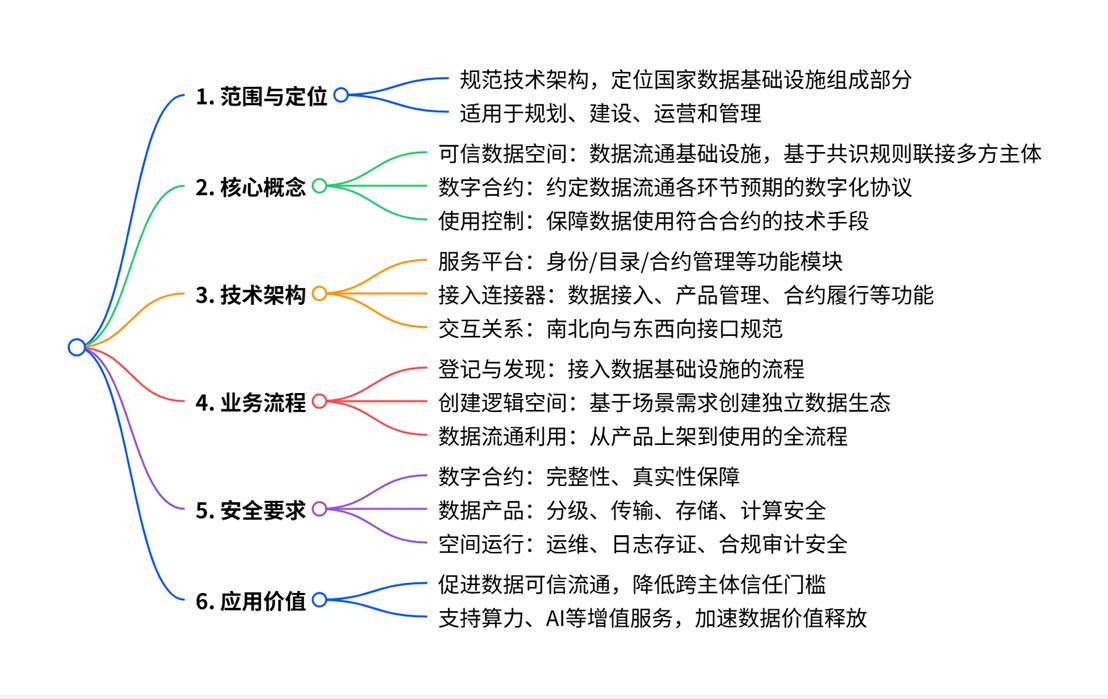

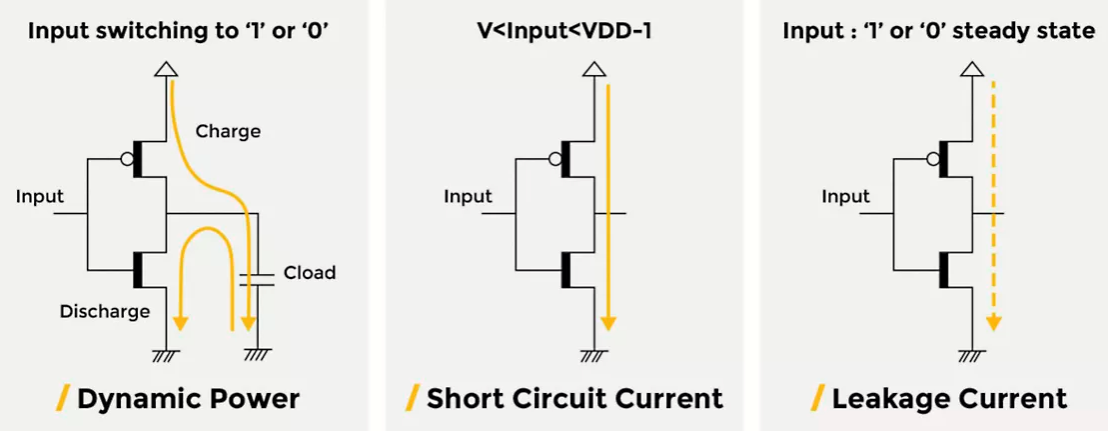

图 1. 互补金属氧化物半导体 (CMOS) 电路中的电源组件

为了实现低功耗设计,设计人员必须降低每个构成总功耗的单个元件。图 1 显示了动态和静态功耗特性。互补金属氧化物半导体 (CMOS)反相器的动态充电使功耗与时钟频率成正比。晶体管在无活动状态下的漏电功率构成静态功耗。

低功耗设计人员可以通过控制电源电压、降低电路复杂性和时钟频率以及监控直流电流源和开关节点电容来降低总功耗。一切都是互联的,因此设计人员必须通过测试和使用低功耗设计技术来权衡这些因素,以优化设计性能。

低功耗设计技术和最佳实践

时钟门控

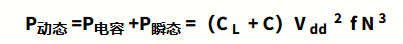

降低设备功耗的一种方法是在寄存器传输 (RTL) 级别调整设计。这是降低动态功耗最常用的技术之一。在 RTL 级别,晶体管改变逻辑状态或为负载电容充电时都会消耗功率。总动态功耗为:

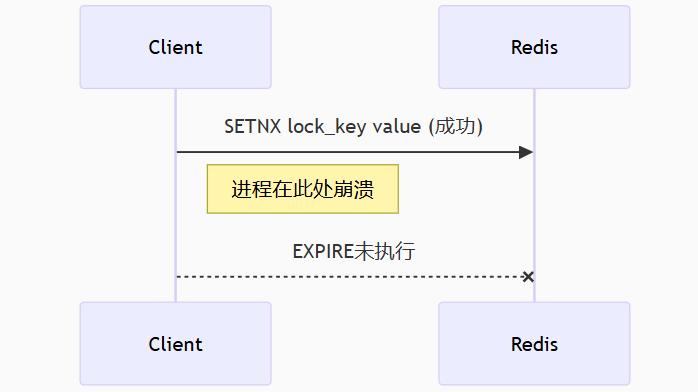

电源门控

IC 中的所有模块并非始终处于工作状态;这取决于它们在设备中的应用。如果某个模块在特定情况下不工作,则无需为其供电。通过关闭非工作模块的电源,可以降低功耗。为了有效地利用这项技术,设计人员可以使用隔离模块来阻止来自电源门控模块的不必要信号。

频率门控

众所周知,芯片由多个模块组成,每个模块并不需要最高的工作频率。最好的技术是根据模块的频率要求进行隔离,并为不同的模块提供不同的时钟信号。这种方法可以大大降低IC的局部动态功耗。

多电压设计

设计中每个模块的运行功耗各不相同。您可以根据模块的性能及其电压要求对芯片进行分区。电压要求越高,功耗就越高。通过创建具有不同电压输入的电压岛,可以轻松降低IC的整体功耗。

动态电压和频率调节

电压岛技术存在局限性——一旦设计好某个模块的电压供应,之后就无法更改。 动态电压调节技术为设计人员提供了灵活性,可以根据需求稍后更改电压。设计人员可以对调节器进行编程,根据电流变化改变各个模块的电源供应。同样,电压调节可以与频率调节相结合,使设计人员能够借助软件程序修改提供给每个模块的时钟信号。

降低功率

迄今为止,最重要的功耗降低技术是降低芯片的电源电压。动态开关功率在FinFET设计中占主导地位,并且与电源电压的平方成正比,因此极力推崇超低压(ULV)工艺。

漏电功率权衡

漏电是 FinFET 前技术中的一个重要功耗问题,最好使用多 Vt 库来控制。这些库为每个单元提供两个或三个版本,每个版本的性能/漏电权衡各不相同。这使得设计人员可以在时序关键路径中使用快速、漏电的单元,而在不太关键的路径中使用速度较慢、漏电较低的单元。

总的来说,有很多技术可以用来降低集成电路的功耗。通过实施这些技术并使用合适的设计和仿真工具,设计人员可以克服这些挑战。Ansys RedHawk-SC等工具使工程师能够在每个设计阶段仿真和预测设计行为,从而设计出更节能、电池寿命更长的低功耗集成电路。

低功耗设计挑战

- 电压降裕度变得非常严格,尤其是在超低压设计中。这种演变使得电压 (IR) 降签核验证成为所有现代 IC 设计的重要组成部分。

- 低电源电压使路径时序更容易受到动态电压降 (DVD) 的影响。此外,要充分分析 DVD 以捕捉所有可能的开关场景也极具挑战性。仔细的电压降分析对于最大限度地降低 DVD 对时序的影响并避免因意外的电压降影响而导致频率损失至关重要。

- 多电压区域需要精心管理,以确保不同电压区域之间的信号转换和完整性。UPF 正是为应对这一挑战而设计的标准。

- 当再次打开一个块时,电源门控会引入具有挑战性的转换现象 - 电气和逻辑。

- 时钟门控在尽可能靠近时钟分配网络根部的位置实现时效率最高,但这会受到使能信号时序可行性(如果信号能够准时到达)的限制。这需要权衡已实现的功率效率和设计优化工作量。

任何功耗分析的有效性都高度依赖于电路活动。然而,要生成一个真实且具有代表性的活动场景,捕捉所有模式下实际使用中可能出现的所有功耗状况并非易事。一个常见的错误是使用功能验证活动向量来计算功耗;这些向量具有误导性,且与功耗分析无关。良好的活动向量可以手动生成,也可以由功耗工具自动生成(“无向量”),或者通过运行实际应用程序的硬件仿真器生成。

参考资料:

https://www.ansys.com/blog/low-power-ic-design-techniques-best-practices