最近看到一句很有意思的话:

每一次科技变革,都是对整体产业链的颠覆与重构。

如果说是因为人类史上的第三次革命造就了我们现在的生活,那么对于第三次革命的核心——半导体产业而言:

变革还在继续,且将不断持续下去。

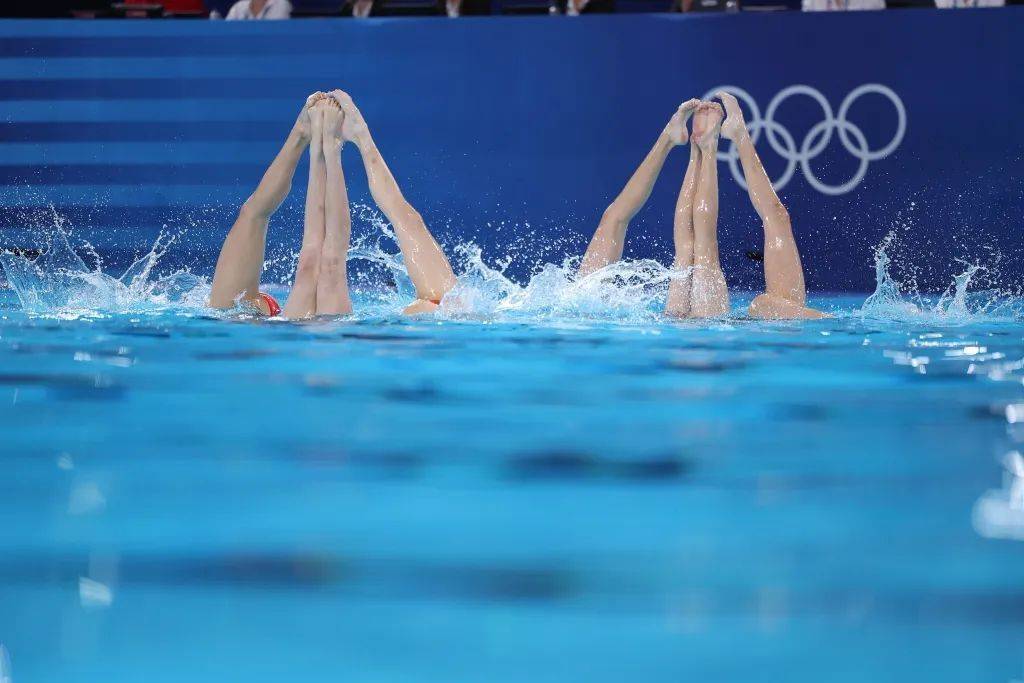

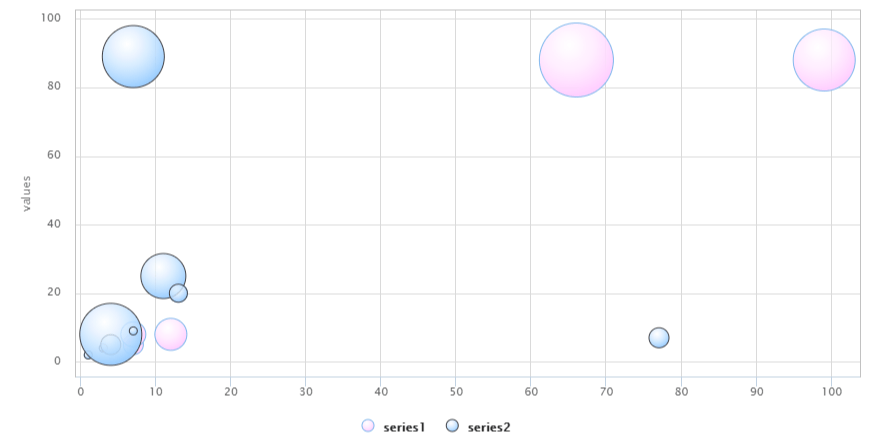

图片来自:应用材料(AMAT.US)业绩会纪要

图片来自:应用材料(AMAT.US)业绩会纪要

或许,在之前的几十年间:

半导体PPACt(晶片功率、效能、单位面积成本及上市时间)路线图一直是通过2D平面缩小和单片半导体集成实现的,并且节奏相对比较固定。

在此期间,半导体封装通常被视为该行业中低价值部分;

它的主要功能是保护芯片并能够将芯片连接到印刷电路板(PCB),然后在PCB板上完成各芯片和各模块之间的电源和信号连接。

当时间跨入2016年以后,变革来临了:

相关从业者在各种各样的行业新闻中,应该都可以看出:

从晶圆代工厂到封装厂再到IC设计公司和系统厂商,都开始将先进封装作为延续摩尔定律的一个突破口。

随着计算从个人电脑到移动设备的发展,又到如今的人工智能时代,封装的作用发生了巨大变化。

先进封装作为晶圆制造的后道工序,在持续压缩芯片体积,提高加工效率,提升设计效率和降低成本上不断发挥重要作用。

相比于传统封装,先进封装具有提升芯片功能密度,缩短互联长度和进行系统重构三大功能。

来自abbrevaitionfinder

来自abbrevaitionfinder

这其中,RDL(Re-distributed layer,重布线层)技术的运用功不可没。

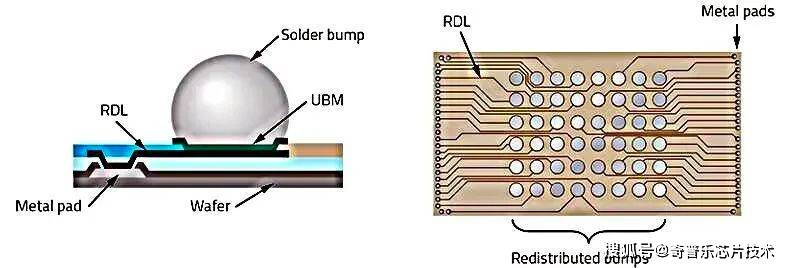

RDL(ReDistribution Layer)重布线层,起着XY平面电气延伸和互联的作用。

来自于《SiP与先进封装技术》

来自于《SiP与先进封装技术》

在芯片设计和制造时,IO Pad一般分布在芯片的边沿或者四周:

IO pad是一个芯片管脚处理模块,即可以将芯片管脚的信号经过处理送给芯片内部,又可以将芯片内部输出的信号经过处理送到芯片管脚。

这对于Bond Wire工艺来说自然很方便,但对于Flip Chip来说就有些勉为其难了。

因此,RDL就成为了此时的关键钥匙:

在晶元表面沉积金属层和相应的介质层,并形成金属布线,对IO端口进行重新布局,将其布局到新的,占位更为宽松的区域,并形成面阵列排布。

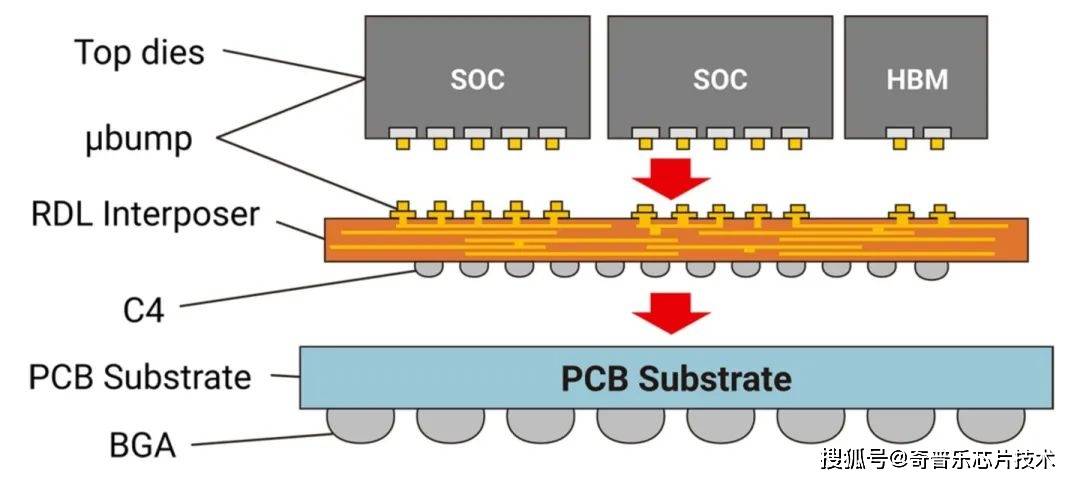

来自于台积电官网(CoWos-R)示意图

来自于台积电官网(CoWos-R)示意图

在先进封装的FIWLP (Fan-InWaferLevel Package) 、FOWLP (Fan-Out WaferLevel Package) 中:

RDL是最为关键的技术。

也正是这项技术的兴起,使得封装厂得以在扇出型封装技术上与晶圆厂一较高下。

通过RDL将IOPad进行FIWLP或者FOWLP,形成不同类型的晶圆级封装。

在FIWLP中:

bump全部长在die上,而die和pad的连接主要就是靠RDL的metal line,封装后的IC几乎和die面积接近。Fan-out,bump可以长到die外面,封装后IC也较die面积大(1.2倍)。

FOWLP是:先将die从晶圆上切割下来,倒置粘在载板上(Carrier)

此时载板和die粘合起来形成了一个新的wafer,叫做重组晶圆(Reconstituted Wafer);在重组晶圆中,再曝光长RDL。

特别是在2.5D先进封装中,除了硅基板上的TSV,RDL同样不可或缺:

来自台积电的InFO(集成扇出)晶圆级封装

来自台积电的InFO(集成扇出)晶圆级封装

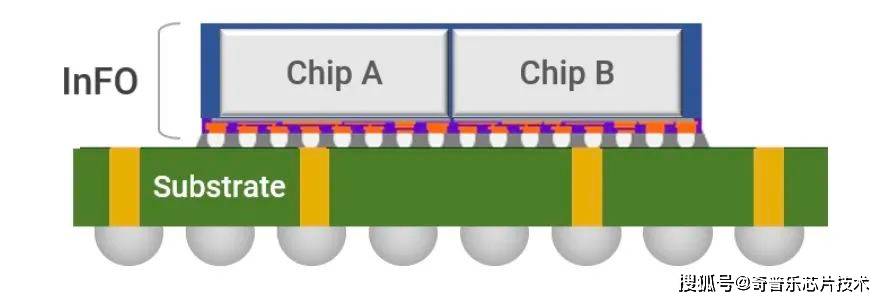

以台积电的2.5D先进封装的代表InFO为例:

InFO 在载体上使用(单个或多个)裸片,随后将这些裸片嵌入molding compound的重构晶圆中。

随后在晶圆上制造 RDL 互连和介电层,这是“chip first”的工艺流程。

单die InFO 提供了高凸点数选项,RDL 线从芯片区域向外延伸——即“扇出”拓扑。

讲到这,我们也应该也对RDL技术有了一定的了解。

放眼未来:

RDL工艺的出现和演变也和TSV等先进封装其他工艺一样,是一个不断演变与进化的过程。

但,当下可知的是:

RDL工艺的诞生,已经为先进封装中的异质集成提供了操作上的基础。

本次的RDL工艺我们就先讲到这儿~

想了解更多半导体行业动态,请您持续关注我们。

奇普乐®️将在每周,不定时更新~

最后的最后,借用马卡连柯的名言:

即使是最好的儿童,如果生活在组织不好的集体里,也会很快变成一群小野兽。

愿每一位半导体从业者可以——

促融合,常发展!