引 言

随着电子信息技术的不断进步,人工智能、医

疗器械、机器视觉等领域都在高速发展 [1] ,工业相机

是机器视觉系统中的一部分 [2] ,对工业相机而言,传

输图像的速率、传输过程的抗干扰能力是其关键,

工业相机需在特定环境下持续工作,高速视频传输

技术在此场景下至关重要。

FPGA ( Field Programmable Gate Array ),现场

可编程门阵列器件内部含有丰富的可编程逻辑结

构,具有数据并发处理、数据实时处理、高速传输接

口等特点 [3] ,使其在图像采集领域得到了广泛的应

用。国内外在图像传输过程中采用以太网作为传

统传输方案,但该技术存在丢包率高的问题,部分

系统转向非标准化协议导致其不易推广,在缓存方

面,采用 RAM ( Random Access Memory ),使得传输

速率大大降低。 GTH ( Gigabit Transceiver )高速串

行收发器具有低功耗、高速数据传输、时钟恢复等

特点 [4] ,可以实现 10 Gbps 以上的传输,因此, GTH

在图像传输、通信等领域得到广泛应用。文中针对

工 业 相 机 传 输 速 度 慢 、传 输 质 量 差 等 问 题 ,采 用

Xilinx ZYNQ UltraScale+ 系列芯片,结合 GTH 收

发器实现对图像数据的高速采集传输系统。

1 系统总体方案设计

系 统 使 用 Xilinx 公 司 型 号 为 XCZU5EV ⁃

2SFVC784I 的 ZYNQ UltraScale+ 系列芯片。芯片

PS 端 集 成 四 个 ARM Cortex ™ ⁃ A53 和 两 个 ARM

Cortex™⁃R5 处理器 [5] 。

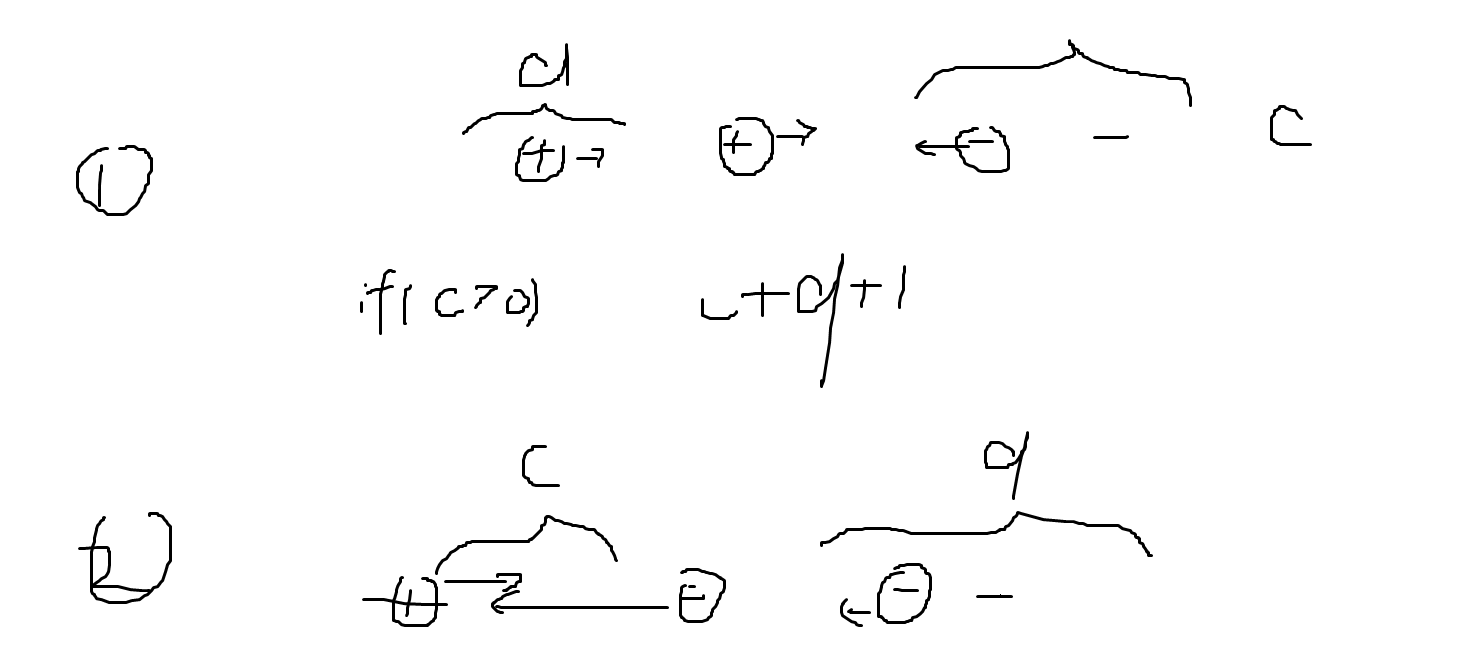

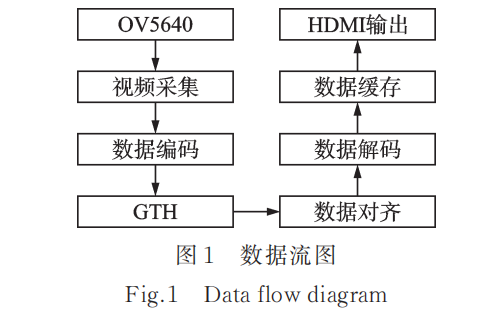

数据流图如图 1 所示。系统使用 OV5640 作为

图像采集模块,像素配置为 RGB565 格式, PS 端对

SCCB ( Serial Camera Control Bus )总线进行参数配

置 , FPGA 进 行 DVP ( Digital Video Port )图 像 采

集 [6] 。 OV5640 采集的图像数据经过 FIFO ( First In

First Out )缓存后输出到板载的 GTH 光口,对视频

数据进行回环高速传输,传输结束后,对传输过程

中由于频率误差导致的偏移进行对齐,将对齐后的

数据通过 FIFO 缓存传入 DDR4 ( Double Data Rate )

缓存单元中。根据需要从 DDR4 中读取图像数据到

HDMI ( High Definition Multimedia Interface )模 块

显示。

2 核心模块设计

2.1 视频采集模块

系 统 使 用 OV5640 采 集 图 像 信 息 ,最 高 具 有

2 592×1 944 的分辨率,最高支持 500 万像素的分辨

率输出,具有白平衡调节、降噪等功能。 OV5640 输

出 支 持 DVP 接 口 ,选 取 DVP 接 口 时 , AVDD 和

DOVDD 的供电需求为 2.8 V , DVDD 供电需求为

1.5 V [7] 。 控 制 接 口 为 SCCB 接 口(兼 容 IIC )。

SIO_C 为输入管脚, SCCB 的时钟线, SIO_D 为 IO

管脚, SCCB 的数据线。

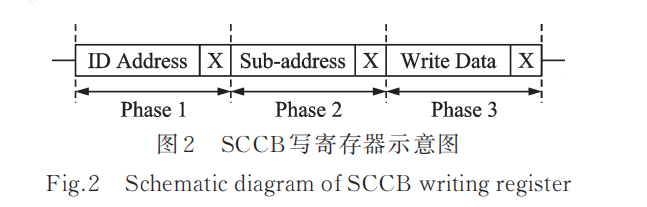

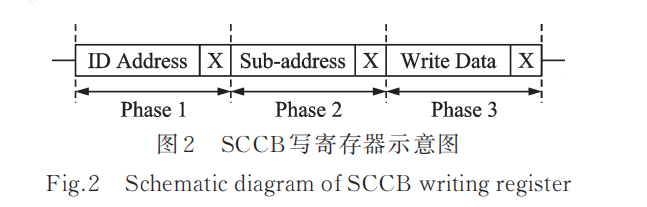

SCCB 写寄存器的示意图如图 2 所示。 ID Ad⁃

dress 表示器件地址和读写位, Sub⁃address 表示 16

位寄存器地址包含高字节和低字节, Write Data 表

示写数据[8] 。

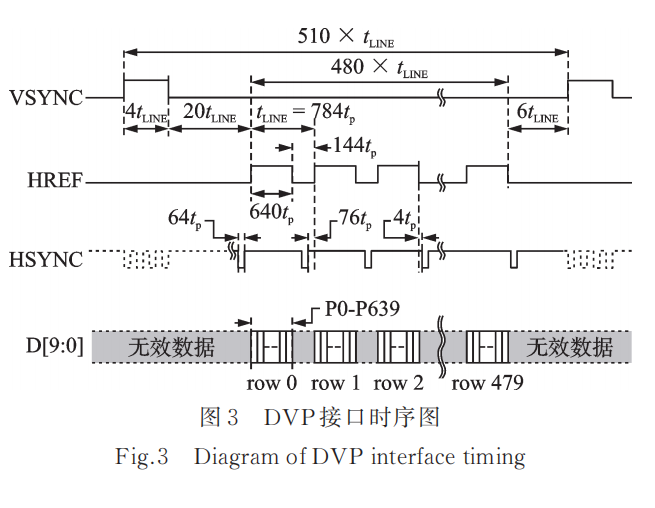

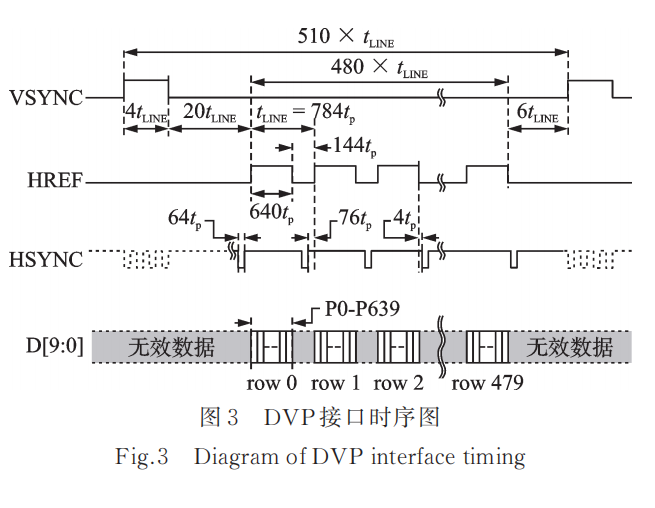

DVP 接口时序如图 3 所示。 VSYNC ( Vertical

Synchronization )为场同步信号, VSYNC 高电平期

间 输 出 一 帧 图 像 数 据 。 HSYNC ( Horizontal Syn⁃

chronization )为行同步信号, HREF 为高电平时直接

输出像素数据。

2.2 数据编码解码模块

视 频 数 据 以 HS 、 VS 、 DE 、 RGB 格 式 输 入 [9] ,

GTH 传输的数据为高速串行差分信号,因此需要进

行以下处理。 GTH 的发送入口为 32 位,需要将 24

位的 RGB 数据先转化为 16 位的 RGB 数据,再由 16

位的 RGB 数据转换为 32 位的 RGB 数据。将视频

数据的 VS 、 DE 、 RGB 数据处理为 32 位的并行数据,

并准备输入给 GTH 的发送端口。使用 FIFO 实现

16 位转换 32 位。当 VSYNC 达到上升沿时,发送场

同步开始帧头,编码为 32 ’ h55_00_00_bc 和 32 ’ h55_

00_01_bc ,当 FIFO 中的数据量没达到要求时发送

无效数据,编码为 32 ’ h55_00_02_bc 和 32 ’ h55_00_

03_bc ,当 FIFO 中的数据有一定量时,发送有效数

据开始帧,编码为 32 ’ h55_00_04_bc ,当一行数据发

送完成时发送有效数据结束帧,编码为 32 ’ h55_00_

05_bc ,当 VSYNC 达到下降沿时,发送场同步结束

帧 尾 ,编 码 为 32 ’ h55_00_06_bc 和 32 ’ h55_00_

07_bc 。

数据解码模块是将进行拼接处理后的数据进

行解析,将解析后的数据存入到 FIFO 中进行缓存,

与数据编码模块相似。

2.3 GTH 模块

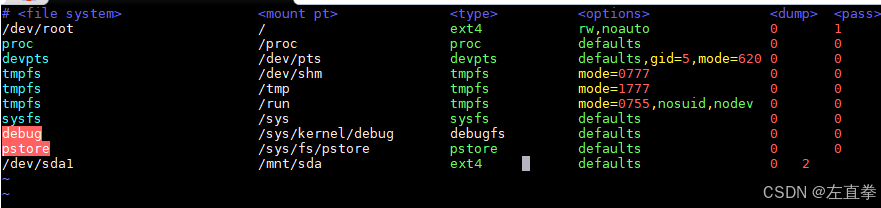

系统选用的为 Xilinx 的 ZYNQ UltraScale+ 系

列 的 开 发 版 ,开 发 板 为 AXU5EV ⁃ P ,芯 片 型 号 为

XCZU5EV⁃2SFVC784I ,该芯片具有 4 对 GTH 串行

高 速 收 发 器 ,最 高 传 输 速 率 可 达 到 16.3 Gbps [10] 。

AUX5EV⁃P 开发板上,有 2 路光纤接口 SFP1~SFP

2 ,连 接 在 FPGA 芯 片 的 GTH 的 通 道 上 。 其 中

SFP1 光 模 块 接 口 连 接 到 GTH 的 Channel0 上 ,

SFP2 和 GTH 的 Channl1 相 连 接 。 光 模 块 的

TX_Disable 信 号 和 RX_LOSS 连 接 到 FPGA 的 普

通 IO 口上。 TX_Disable 信号用来使能光模块的发

射,如果 TX_Disable 信号为低,发送使能,否则发送

关闭,正常使用时信号为低 [11] 。

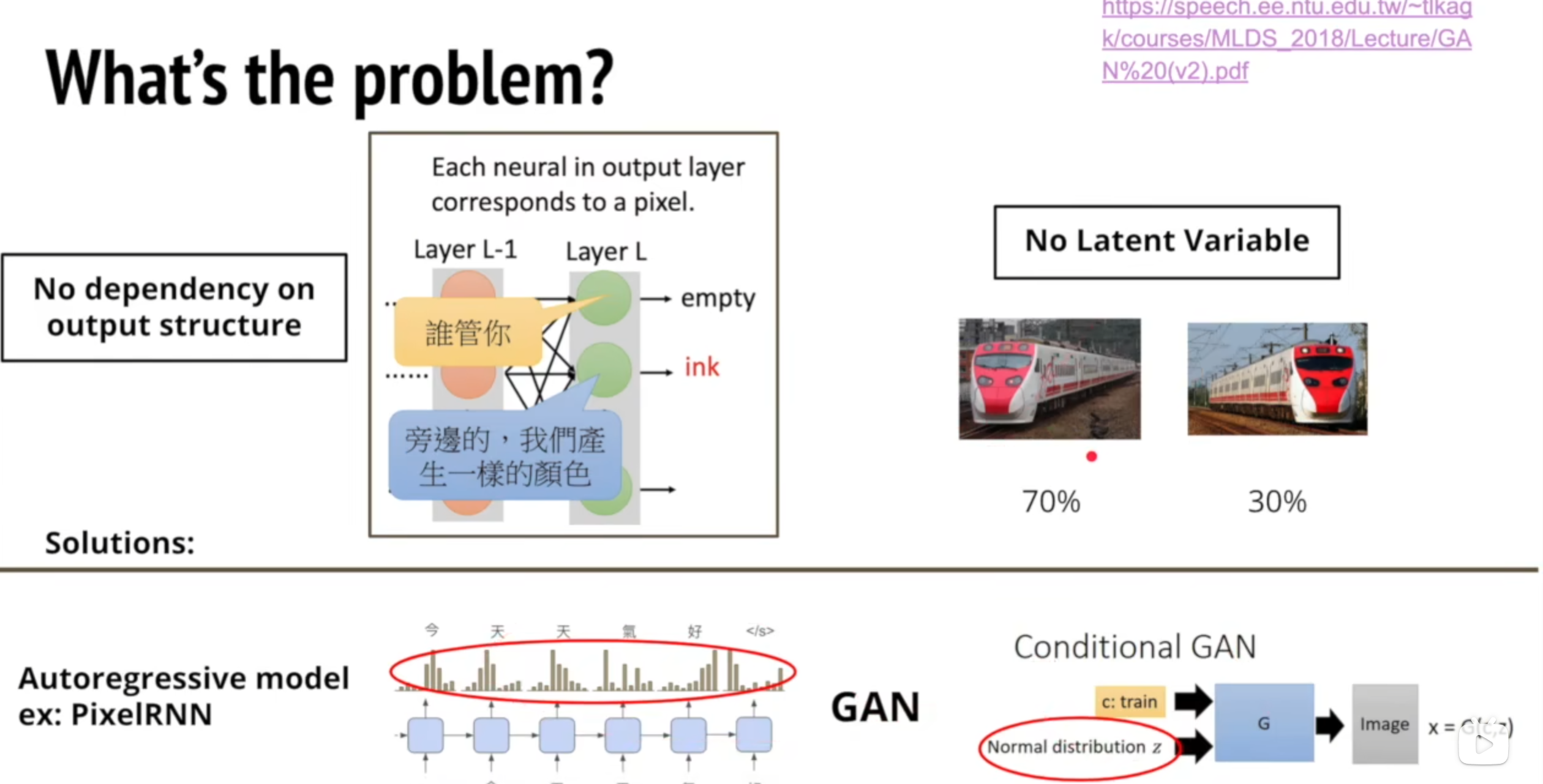

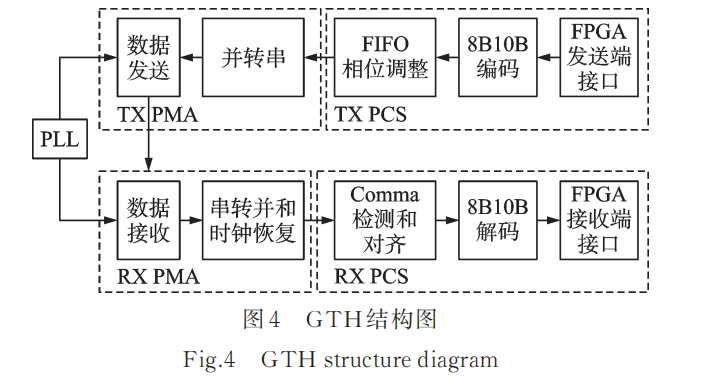

GTH 结构图如图 4 所示。发送器由一个 PCS

( Physical Coding Sublayer )和 一 个 PMA ( Physical

Medium Attachment )组成 [12] ,数据从 FPGA 逻辑流

入 FPGA 的 TX 接口,通过 PCS 和 PMA ,然后作为

高速串口从 TX 驱动器流出。接收器同样由一个

PCS 和 PMA 组成,高速串行数据流入 GTH 收发器

RX 的 PMA ,进入 PCS ,最后流入 FPGA 逻辑。其

中 PCS 负责串化和解串化, PMA 负责数据流的编

码解码,能够实现时钟恢复、线路编码 (8B10B) 、预加

重等功能 [13] ,可以减小信号衰弱、时钟扭曲。

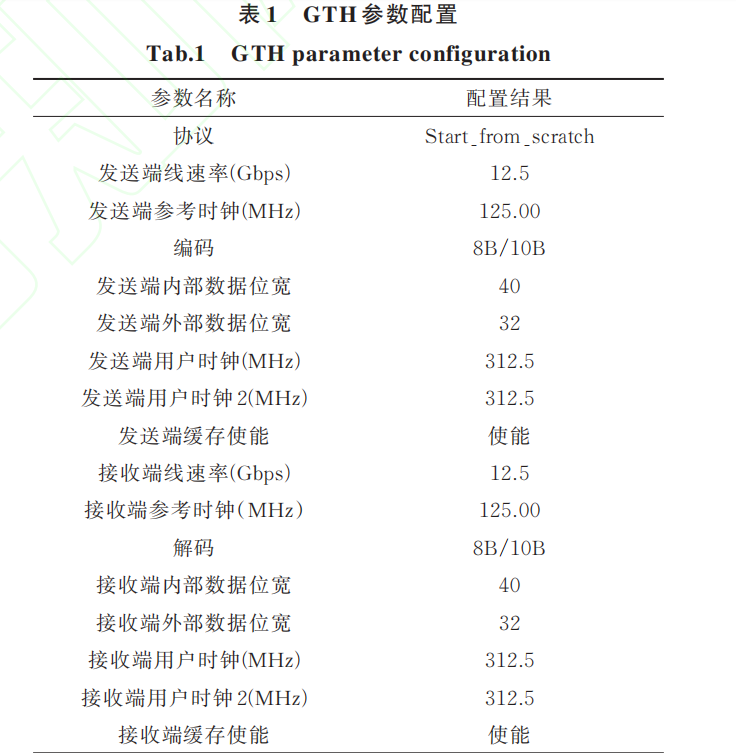

系统使用 Vivado 内部的 GTH Transceivers IP

核。 GTH 端口支持多种通信协议,包含但不限于

SATA 、 aurora 8B10B 等,文中选择无协议模式自定

义参数,包括通信速率、参考时钟选择、编解码方

式 、 Comma 值 设 定 等 。 GTH 配 置 参 数 如 表 1

所示。

应用程序通过在发送端用户时钟上升沿的时

候将数据写入 TXDATA 端口,通过 GTH 收发器传

输数据。传入的数据经过 8B10B 编码后,进入一个

发送缓存区,该发送缓存主要是将 PMA 层和 PCS

层两个时钟隔离,解决两个子层的时钟速率相位差

异和速率匹配问题,最后经过高速 GTH 进行并串

转换,根据自己的需要选择预加重、去加重、极性转

换等功能,接收端存在弹性缓冲区,具有时钟纠正

和通道绑定功能,其余和发送端类似。

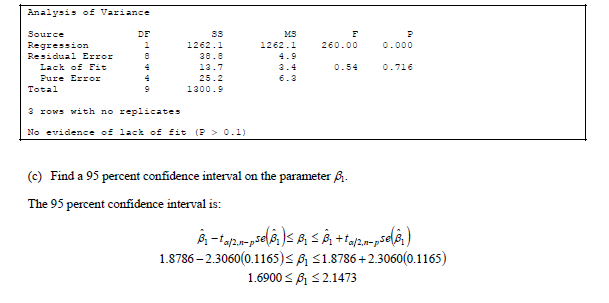

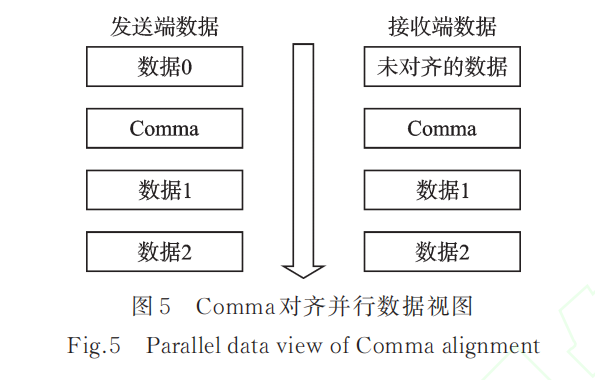

2.4 数据对齐模块

GTH 在高速传输数据的时候,由于不同的系统

时钟之间造成的频率误差,数据可能会发生错位,

例如 32 位数据的低 x 位数据和下一个 32 位数据的

高 (32- x ) 位数据拼接在一起,从而发生移位的情

况。为了校准,发送端需要发送一个可识别的序

列, Comma 码。接收端在收到 Comma 码时,需要将

Comma 码移动到字节边界,以便接收到的并行字节

和发送的并行字节匹配。 Comma 对齐的并行数据

视图如图 5 所示。

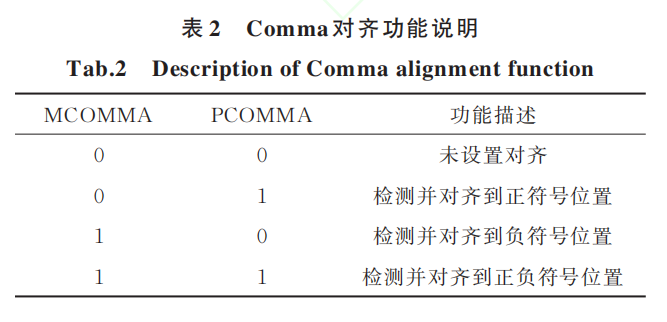

Comma 是 8B10B 编码中内容,在 8B10B 编码

方案中会有 +1 和 -1 两种状态,也被称为极性偏

差。当 K 码设为 K28.5 后,由于 8B10B 编码的极性

问题,会出现两种编码结果,互为按位取反关系,分

别 称 为 MCOMMA ( Minus Comma )和 PCOMMA

( Plus Comma )模式,也就是 -1 和 +1 ,检测器可以

对编码进行对齐, Comma 对齐功能说明如表 2 所

示。文中选用第四种模式,检测到正、负符号时对

齐到该符号位置。

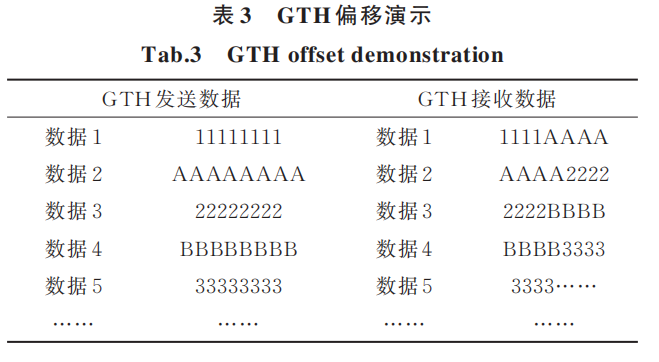

GTH 收 发 器 外 部 用 户 数 据 接 口 的 宽 度 为 32

位,内部数据宽度为 40 位。在实际测试中,发送的

32 位数据有时候会出现 16 位的数据偏移情况,就是

说发送和接收的数据会出现 16 位的偏移, GTH 偏

移演示如表 3 所示。

信迈提供ZYNQ软硬件控制器定制服务。

![[定昌linux开发板]设置密码策略](https://i-blog.csdnimg.cn/direct/b848d84c4aae448a8e818ea0e67a95a9.jpeg)