通道均衡已成为当今高速串行链路的关键机制。目前有许多均衡方案,例如发射机加重均衡、接收机CTLE(连续时间线性均衡器)、FFE(前馈均衡器)、DFE(判决反馈均衡器)和FEC(前向纠错),这些方案可以在链路的不同位置设计和使用。虽然这些均衡方案有一些通用的理论,但其实际用途、实现方式、约束条件,以及最重要的,这些均衡组件对各种通道干扰的有效性,却鲜为人知或有文献记载。此外,随着数据速率达到112Gbps及以上,以及收发器电路设计和半导体工艺节点的进步,这些均衡方案在实施过程中,其复杂性和成本方面将会发生或将会发生改变。

本文将解释并研究上述每种均衡器 (EQ) 方案的理论、实现、约束条件和成本。然后,我们将定量分析每种均衡器方案针对信道弊端的有效性。性能矩阵将由模拟图的高/宽、信噪比 (SNR) 等参数给出,这些参数是通过使用真实信道进行设计实验得出的。

- 信道均衡方案的理论和原理:发射机预加重/去加重,接收机CTLE、FFE、DFE和FEC。

- 每个 EQ 方案的实施、约束和成本:我们比较了各种类型的 EQ 实施技术,例如模拟和基于 ADC 的设计及其权衡。

- EQ 有效性分析:我们将从通道特性、噪声处理和 EQ 配置方面进行实验设计,以检查每种 EQ 方案的性能。

最后,我们将通过查看链接级别的发现和结果来总结研究,并对链接设计进行交易分析。

信道均衡方案概述

当 PCISIG 推出数据速率为 5.0Gbps 的第二代 PCI-Express 标准时,有线线路通道均衡开始成为高速 I/O (HSIO) 链路的典型特性。PCI-Express 第二代链路中提供了发射器增强功能。此后,HSIO 数据速率每 2 到 3 年翻一番 [1]。通道均衡技术已成为速度增长的关键支持技术 [2][3]。在当今最先进的 50~56Gbps 串行链路设备中,我们可以发现各种类型的均衡方案被部署。

信道均衡方案的主要目标是提高链路末端的信噪比 (SNDR)。其原因在于我们希望通过在接收器中使用数据限幅器来恢复从源头传输的信息。由于传输波形会受到信道分量的扭曲和衰减,例如符号间干扰 (ISI)、抖动 [4](由通信介质带宽、参考源和时钟分配网络的时序偏差以及来自串扰电源和电源分配网络的噪声 [4] 引起),均衡器的作用是将这些非理想因素最小化,以便接收器能够以更高的置信度检测和恢复信息。

发射机 (TX) 强调

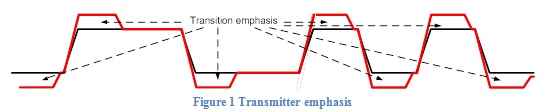

TX 加重是一种模拟波形处理方法,可在转换时引入受控峰值。实际上,该方案使用高通滤波器对 TX 输出波形进行预处理,该滤波器的特征在于峰值和肩部之间的电压差以及波形峰值部分的持续时间(参见图 1)。具体实现方式是,当峰值信号添加到原始 TX 输出波形中时,如果峰峰值幅度大于原始未加重波形,则称为 TX 预加重。另一方面,如果抑制 TX 输出波形的肩部,同时保持相同的峰峰值幅度,则称为去加重。

TX 加重通常不随链路速度变化,因为峰值持续时间由 TX 的驱动电路设计固定,峰值由每次数据转换触发。因此,它在固定数据速率范围内有效,而当链路数据速率远离设计目标频率时,其均衡性能会下降。此外,补偿只能应用于主光标。TX 加重由于其独特的特性,可以提供子光标通道补偿,其中峰值频率可以高于 TX FIR 方法(见下文)。

发射机FIR

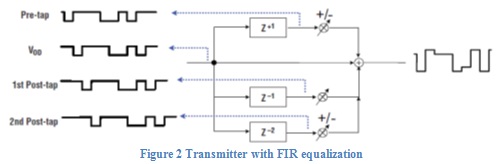

TX FIR 的全称是“带 FIR EQ(有限脉冲响应均衡器)的发射机”。TX FIR 使用 FIR 滤波器进行均衡,并与发射机时钟同步,如图 2 所示。与 TX 加重方案相比,TX FIR 具有以下几个优势:

- 由于 FIR 由时钟驱动,因此 TX 均衡与链路数据速率成比例

- 多抽头FIR可以更好地补偿不同的信道特性

- TX FIR 可以补偿前光标和后光标的 ISI

从实现角度来看[5],TX FIR 比 TX 加重更复杂,并且需要时钟源。TX FIR 通常受峰值功率限制,最大输出幅度将被限制在非均衡幅度水平。由于峰值功率限制,TX FIR 会降低有效平均输出幅度,从而减少链路末端接收到的能量。

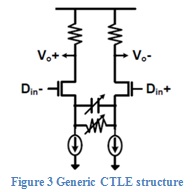

RX CTLE

RX CTLE 代表接收器连续时间线性均衡器。RX CTLE 电路 [6] 具有频率响应,可以补偿或反转通道的频率响应(参见图 3)。如果设计得当,它将产生相对平坦的频率响应,从而将接收信号恢复到其原始形式。RX CTLE 可以是有源的,它可以增强输出信号的幅度;也可以是无源的,它可以衰减输入信号的低频成分。有源和无源 CTLE 设计各有优缺点。例如,有源 CTLE 设计通常可以提高信噪比 (SNR),但可能受到直流增益压缩等非线性行为的影响。无源 CTLE 设计通常是线性的,但输出信号电平更小。

CTLE 能够补偿前光标和后光标的 ISI,并且通常具有较高的功率效率。电路设计人员可以设计出可调的 CTLE,其交流增益和直流增益可以调整,以匹配信道特性。由于这些特性,CTLE 几乎存在于所有 HSIO 接收器设计中。

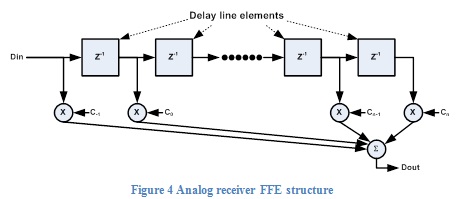

接收 FFE

RX FFE 代表接收器前馈均衡器。理论上,RX FFE 等同于 TX FIR,因为它们都是基于 FIR 且为线性均衡器 [6]。当在模拟域中实现 RX FFE 时,需要一系列延迟线,用于缓冲输入信号,并根据 FFE 系数进行相加或相减(参见图 4)。此外,FFE 也可以在比特级或符号级实现,其中均衡是通过 FFE 系数与采样输入数据流的符号级卷积来完成的。RX FFE 通常与自适应方案配合使用,其中 FFE 系数源自信道特性。虽然 RX CTLE 和 FFE 都是线性均衡器,但 FFE 的自适应特性使其在处理各种信道时更加灵活。

RX FFE 的设计、实现和使用成本在很多方面都更高。首先,FFE 需要时钟才能运行。这意味着接收器要么能够从输入信号中恢复时钟时序,要么知道链路的工作频率。这对于模拟 FFE 设计来说尤其具有挑战性。我们将在以下章节中进一步讨论。

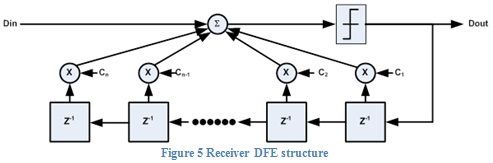

接收数据反馈

RX DFE 代表接收器判决反馈均衡器。DFE 采用 IIR(无限脉冲响应)结构,其中利用 DFE 系数调整的先前判决(由限幅器模块确定的数据符号)之和来最小化目标符号级的误差(参见图 5)。与上述 EQ 方案相比,DFE 具有几个明显的优势:首先,由于其 IIR 结构,对于某些信道特性,DFE 可以用相对较短的抽头长度校正大量的 ISI。其次,由于判决结果不受噪声影响,DFE 能够补偿信道 ISI,而不会放大来自链路和设备的噪声。

与 RX FFE 一样,DFE 也需要时钟才能运行。因此,它在实现和运行方面比 CTLE 更昂贵。此外,由于采用反馈方案,一旦做出错误决策,DFE 也容易出现突发错误,因为这会导致输出端出现连续错误。突发错误会影响前向纠错 (FEC) 的性能。我们将在后续章节中进一步讨论这个问题。

前向纠错(FEC)

当数据速率达到 25Gbps 及以上时,前向纠错 [7] 已成为串行链路的重要组成部分。原因在于,仅靠均衡方案实现 10 -12或 10 -15的期望 BER 变得更具挑战性(尤其是在时序预算不断缩减且接收端接收信号较小的情况下)。如果链路中仅存在随机错误,或者存在突发错误,则 FEC 可以将 SNR 或 BER 提高 10 4到 10 9倍,而如果链路中存在突发错误,则提高幅度会更小。

PLL 以及时钟和数据恢复 (CDR)

PLL 和 CDR 通常不被视为串行链路中 EQ 方案的一部分。然而,它们对串行链路的性能至关重要。参考串行链路抖动和噪声分类 [4],PLL 和 CDR 是唯一能够补偿正弦抖动 (SJ)、有界不相关抖动 (BUJ) 和随机抖动 (RJ) 的机制。如果进一步关联到当今的 HSIO 挑战,这些抖动分量是低 BER 下链路裕度收窄的主要因素。我们不会主动讨论和研究 CDR 和 PLL 在 EQ 性能中的作用,但在开发串行链路时,应该牢记这两个因素。

均衡方案的特点和性能

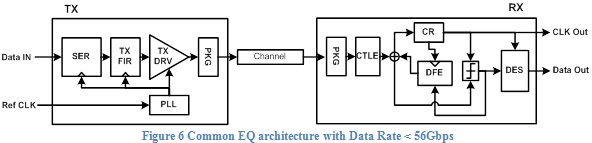

数据速率 < 56 Gbps 的通用 EQ 架构

尽管每个 HSIO 设备的设计各不相同,但现有技术(包括半导体材料、工艺、电路实现以及微观/宏观控制算法)及其成熟度使得整体均衡架构趋于趋同。更具体地说,一个实用或合理的设计必须符合功耗、性能和(芯片)面积 (PPA) 矩阵,以便产品能够有效地制造和部署。

在高速IO链路速度高达50~56Gbps的情况下,大多数收发器都采用以下均衡方案:发射器FIR均衡器、接收器CTLE均衡器、模拟DFE均衡器和模拟CDR均衡器。因此,让我们来检查一下这些EQ方案的PPA矩阵及其性能。EQ结构如图6所示。

德克萨斯州冷红外

性能:TX FIR 可有效补偿 ISI,但存在局限性。它可以补偿前光标和后光标的 ISI,但仅限于比特或波特级别。TX FIR 的缺点包括峰值功率限制(其中重度均衡会降低有效输出幅度)以及抽头长度较短(TX FIR 通常也限制为 2 个前光标抽头和 2 个后光标抽头)。使用 TX FIR 的主要问题在于 FIR 系数的确定。对于不支持反向信道和相关协议的串行链路,TX FIR 系数是固定的,需要在部署前确定。

功耗:TX FIR 功耗低,因为发射端通常可以随时获取时钟时间。TX FIR 可以使用模拟电路或 DAC 实现。

面积:与功率考虑类似,考虑到上述限制,实施 TX FIR 的开销很少。

RX CTLE 和 VGA

性能:CTLE 在均衡中发挥着至关重要的作用,原因有很多。CTLE 采用模拟电路实现,理论上可以匹配或逆转信道在前级和后级部分的损耗特性。它不仅可以提高信噪比,还可以恢复输入信号的幅度。CTLE 的缺点包括:噪声放大(会加剧高频噪声)、PVT(工艺、电压和温度)变化引起的特性变化,以及灵活性不足(设计完成后通常无法调整或改变其特性)。

功率:CTLE 功率效率高,因为它主要在较小的信号区域内运行。

面积:与电源相同,CTLE占用的芯片面积较小。

RX模拟DFE

性能:DFE 可在模拟域中实现,其中输入的波形或信号会根据之前的判决结果和调整后的 DFE 系数进行调整。DFE 需要 CDR 才能正常工作,因为它需要知道时钟时间和恢复的数据符号。然后,需要在单个符号单位间隔时间内计算补偿/调整并将其应用于数据路径。如上一节所述,由于 DFE 采用 IIR 结构且抽头长度相对较短,因此可以提供强大的长尾校正。这使其成为 56Gbps 以下数据速率的最佳设计选择。

功率和面积:严格的时序要求加上延长抽头长度的需要使得模拟 DFE 设计更具挑战性,并且在 56Gbps 数据速率以上时功率和面积效率更低。

其他 EQ 方案

大家可能已经注意到,RX FFE 并非常见的 EQ 功能。让我们进行 PPA 分析,看看它的表现如何。

性能:DFE 只能补偿后光标 ISI,而 FFE 能够处理前光标和后光标信道效应。从本质上讲,FFE 比 CTLE 更灵活,能够适应更多的信道特性。模拟 FFE 可以部署在接收器中,用作主线性均衡器,也可以作为 CTLE 的补充,用于调整和补偿 CTLE 以及设备的 PVT 变化。

功耗和面积:实现模拟FFE颇具挑战性,因为它涉及使用模拟延迟线。众所周知,模拟延迟线会消耗功耗,并且像CTLE一样,容易受到PVT变化的影响。对于支持多种协议或数据速率的收发器,需要可调延迟线设计,这会使情况更加复杂。这也是模拟FFE未能成为常见产品特性的关键原因。

下一代 EQ 架构

随着数据速率的提高,HSIO 设备和组件设计人员面临着不断缩减的时序预算(假设他们使用相同的编码/调制方案或降低信噪比,并假设使用更高级别的编码方案)。无论采用何种方法,对更强大的均衡方案的需求始终存在。

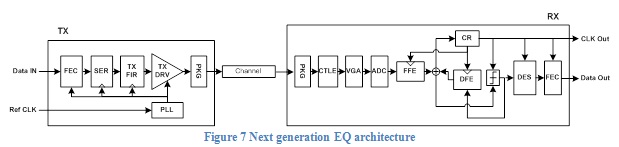

为了处理更复杂的通道特性和均衡方案,设备设计人员开始转向基于ADC的接收器设计。基于ADC的设计优势包括能够使用更精细的均衡和自适应方案,以及延长FFE/DFE抽头长度。然而,随着基于ADC和DSP的均衡设计的加入,不应忽视这种设计方法在面积/功耗、带宽限制和复杂性方面带来的影响(见图7)。

德克萨斯州冷红外

与上一代设计相同。TX FIR 的 PPA 保持不变。

RX CTLE 和 ADC

CTLE 的作用保持不变,因为它旨在执行 ISI 补偿。为什么不使用 ADC 和基于 DSP 的 EQ 来替代 CTLE 呢?要回答这个问题,我们必须了解基于 ADC 的接收器的工作原理。ADC 是一个采样系统,它以符号或子符号速率对输入信号进行采样和数字化。这意味着我们需要知道具有预定 ADC 分辨率的时钟时间。由于大多数接收器必须从输入信号中恢复时钟时间,因此使用 CTLE 将使时序恢复更快、更容易、更稳定。此外,CTLE 将提高 ADC 输入信号的 SDR。这意味着 CTLE 的性能与 ADC 的分辨率之间存在关联。众所周知,基于 ADC 的系统的性能和效率在很大程度上取决于采样率和 ADC 分辨率。在 ADC 之前安装一个功能正常的 CTLE 将大大提高 RX 的整体 PPA 得分。

同样的道理也适用于VGA,它提供输入信号的幅度控制。CTLE可以改善ADC输入信号的SDR,而VGA则通过将输入信号动态范围与ADC的最佳工作范围(即ADC的感测范围和线性度)相匹配来提高SNR。

基于 RX ADC 的 FFE

在 ADC 之后,如果 ADC 以符号率采样一个数据点,则均衡将在符号域中执行。与模拟 FFE 相比,数字 FFE 在数学上更简单、更具可扩展性,因为它是 FFE 系数与采样输入数据之间的卷积。它可以使用流水线结构实现,在保持吞吐量的同时,芯片面积和延迟仅随 FFE 抽头长度线性增长。因此,提供具有长抽头长度的 FFE 成为 PPA 矩阵的可行解决方案,它可以以合理的成本处理远离主光标的反射和阻抗不连续性。

基于 RX ADC 的 DFE

与基于 ADC 的 FFE 相比,基于 ADC 的 DFE 并没有从这种架构变化中获益太多。原因在于,与模拟 DFE 的情况相同,DFE 调整需要计算并应用于数据路径,而数据路径现在由 FFE 调整值表示,并且在一个符号 UI 内。为了满足 DFE 调整计算的时序要求,一种可能的方法是注入额外的延迟周期。基于 ADC 的 DFE 及其相关的延迟注入降低了 DFE 在 PPA 矩阵中的效率。

ADC特异性因素

ADC 的性能对于基于 ADC 的 EQ 架构至关重要。当今最先进的 ADC 设计无法以线速采样数据,因此需要使用一组具有与 ADC 基准时钟相关的固定延迟时间的 ADC,以线速每 UI 采集一个样本。在此过程中,会引入额外的延迟,并导致信号衰减,例如电容负载和噪声。因此,基于 DSP 的 EQ 性能增益的一部分将被这种非理想性和延长的延迟所抵消。

前向纠错

FEC 在 25Gbps 时代开始投入实践,并在 50Gbps 以上的 PAM4 工作条件下展现了其必要性。在 112Gbps 及以上速率下,FEC 有望成为均衡器 (EQ) 架构的重要组成部分。我们的研究 [8] 表明,FEC 的性能取决于接收端切片器的信噪比 (SNR)、由符号间干扰 (ISI) 和 DFE 系数/调整引起的突发错误以及调制方案。下一节我们将进一步讨论 FEC 与均衡相关的性能。

均衡器效果

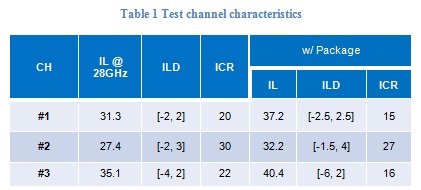

我们使用内部高速链路仿真平台 [9][10][11] 对 112Gbps 的 PAM4 和 PAM8 进行了一系列仿真,以研究不同均衡方案的有效性。本文中展示仿真结果的信道均来自我们的信道数据库(表 1 所示)。这些信道模拟了真实情况,在 28GHz 频率下插入损耗约为 30dB,并具有真实的 ILD(插入损耗偏差)和 ICR(插入损耗-串扰比)特性。

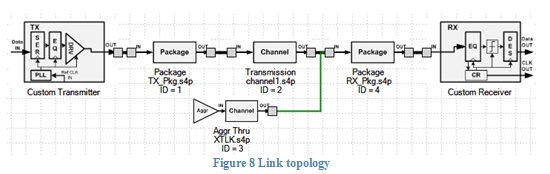

发射器具有以下配置:输出差分幅度 = 1.0V p-p(diff)、20%-80% 上升/下降时间 ≈ 6ps、PAM4/8 电平不匹配 (RLM) = 0.95、回波损耗 ≈ -10dB、TX BUJ(有界不相关抖动)= 0.04UI p-p、TX DCD(占空比失真)= 0.019 UI p-p、TX RJ(随机抖动)= 0.01UI rms和 4 抽头 TX EQ,带有 2 个前光标和 1 个后光标抽头。

接收器具有以下配置:回波损耗≈-10dB、RX CTLE AC 增益从 0 到 20dB、低频 CTLE 增益从 0 到 6 dB、VGA 增益从 0 到 20dB、FFE 具有 3 个前光标抽头和最多 36 个后光标抽头、DFE 具有最多 40 个抽头。

TX 和 RX 封装在 28GHz 时的插入损耗约为2.5dB。链路拓扑如图 8 所示。

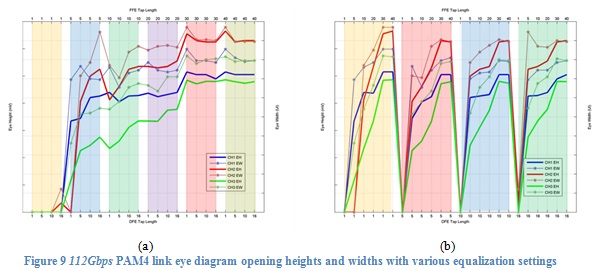

第一个实验是测试 LEQ(线性 EQ,由 TX FIR、RX CTLE 和 RX FFE 组成)和 DFE 在不同配置下的有效性。因为 CTLE 通常是预先确定的,可调性有限,而 TX FIR 和 FFE 在数学上是等价的,所以在本实验中,我们固定 TX FIR 设置并扫描 CTLE 设置,同时调整了 FFE 抽头长度。仿真结果如图 9 所示,其中在 BER = 10 -4时测量了接收器数据切片器的眼图张开高度 (EH) 和眼图张开宽度 (EW) 。为了观察 LEQ/FFE 和 DFE 的有效性,我们以两种不同的方式绘制了仿真图。图 9(a) 绘制了 EH/EW 结果,首先按 FFE 长度排序,然后按 DFE 长度排序。图 9(b) 表示相同的数据,但首先按 DFE 长度排序,然后按 FFE 长度排序。

可以注意到以下几点:FFE 的性能(就 EH 和 EW 而言)与其抽头长度呈良好的线性关系。它随 FFE 长度的增加而呈现近乎单调递增的趋势,并且 DFE 被认为对这些链路起到了补充作用。另一方面,与 FFE 相比,DFE 的均衡效果线性度较低。对于这些信道,无论 DFE 长度如何,至少都需要 5 抽头的 FFE。FFE 和 DFE 之间的一个关键区别是 FFE 能够处理前兆 ISI,这些结果证实并支持了这一理论。此外,FFE 还可用于补偿 CTLE 的不足和/或 PVT 变化。

第二个观察结果是,当 FFE 或 DFE 长度达到约 30 个抽头时,最佳 EH/EW 性能达到饱和。这与信道特性再次吻合:在 PAM4 调制方案下,这些测试信道的显著反射和阻抗不连续性在 112Gbps 速率下均终止于 25 至 30UI 左右。

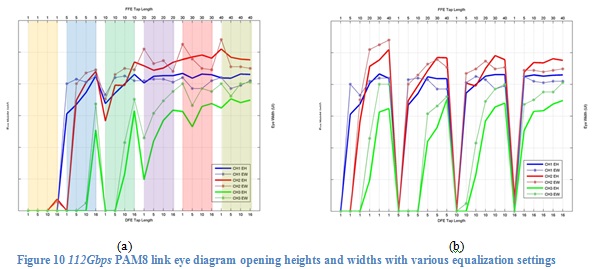

我们还以 112Gbps 的速率,采用 PAM8 调制方案进行了相同的实验,结果如图 10 所示。结果表明,LEQ/FFE 和 DFE 均衡效果呈现出相同的趋势。PAM8 的结果还表明,由于额外的调制级数和调制符号间干扰 (ISI),EH/EW 性能相比 PAM4 进一步下降。虽然 PAM8 调制降低了符号率并减少了带宽消耗,但与 PAM4 相比,均衡需求有所增加。例如,对于信道 #3,最小 FFE 长度大约增加了 5 个抽头,因为 PAM8 需要更复杂的均衡才能达到相同的 BER 性能。

下一个实验是检验均衡方案处理不相关抖动和噪声的能力。不相关噪声是 HSIO 系统中最具挑战性的因素,因为这些噪声通常无法得到有效补偿。最常见的不相关噪声源包括串扰、电源噪声以及转换后的抖动/噪声源(例如,通过限幅放大器产生的抖动/噪声)。众所周知,线性均衡方案(例如 TX FIR、RX CTLE 和 RX FFE)不适用于这些不相关噪声,因为它们往往会放大此类噪声。另一方面,DFE 在处理不相关噪声方面更为有效,因为它采用了判决反馈机制,判决信号不含噪声。

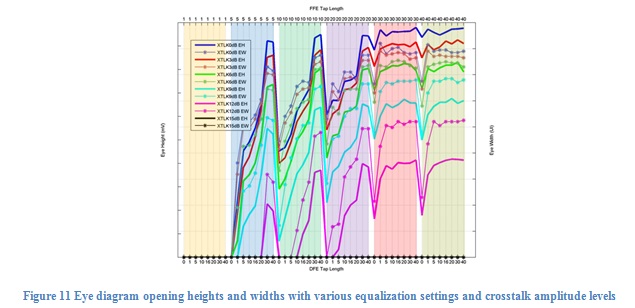

我们进行了一项实验设计,在保持其他所有条件不变的情况下控制串扰幅度。选择通道#3是因为它代表最坏情况通道,因此EH/EW结果不会饱和。EH和EW的仿真结果如图11所示。

我们添加了“无 DFE”情况作为基准,并进一步将 DFE 长度扩展至 40 个抽头,以便进行更清晰的比较。仿真结果提供了一些有趣的见解:首先,串扰不能直接由 FFE 补偿,如 DFE 长度为 0 时的 EH 数据点所示。其次,结果表明,FFE 和 DFE 不能补偿或消除串扰噪声,因为随着串扰幅度的增加,EH/EW 稳步下降,而仿真中 FFE 和 DFE 的系数并未饱和。第三,就增加 EH 而言,DFE 的有效性随着串扰幅度的增加而变得更加明显。最后,当串扰噪声达到原始串扰噪声的 15dB 时,链路不再能达到 BER 10 -4,因此 EH 和 EW 都为零。

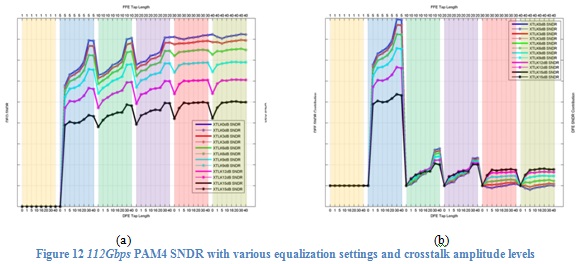

然后,我们观察了图 12(a) 中实验接收器切片器的 SNDR。与图 11 相比,SNDR 图显示了串扰效应,其中最终的最佳 SNDR(即最大 FFE 和 DFE 抽头长度)与链路中的串扰噪声量很好地对齐。15dB 串扰情况,其中链路无法达到 BER 10 -4,仍然可以在接收器的数据切片器中提取 SNDR 数据。我们以无 DFE 情况为基点进一步处理结果,并生成如图 12(b) 所示的图。图 12 显示了一些有趣的因素:首先,只要最小量的 FFE,或者更准确地说,涵盖前光标和后光标 ISI 的线性均衡,DFE 改善 SNDR 的能力就非常显著,尤其是在 FFE 长度较短的情况下。然后,在完全均衡(即使用 30 个 DFE 抽头)的情况下,DFE 将在严重的非相关噪声条件下持续改善 SNDR。最后,结果表明,对于串扰等非相关噪声,我们只需几个 DFE 抽头即可达到最佳效果。

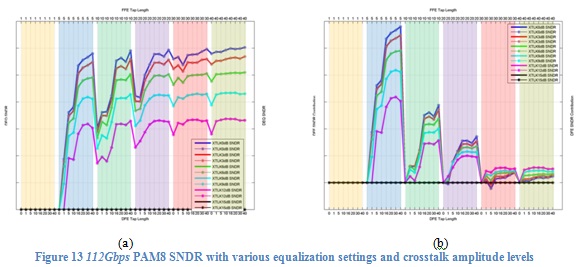

在同一实验中观察到了类似的结果,但采用的是 PAM8 调制方案,结果如图 13 所示。它展现了我们之前看到的相同趋势:PAM8 虽然运行频率较低,但需要更多均衡才能达到其最佳点。需要注意的是,由于 PAM8 的符号电平间隔小于 PAM4,因此 15dB 的情况不起作用,并且无论 EQ 设置如何,RX 限幅器都无法检测或恢复数据。与 PAM4 的情况相同,结果也表明需要一个较短的 DFE 来补偿不相关的噪声。

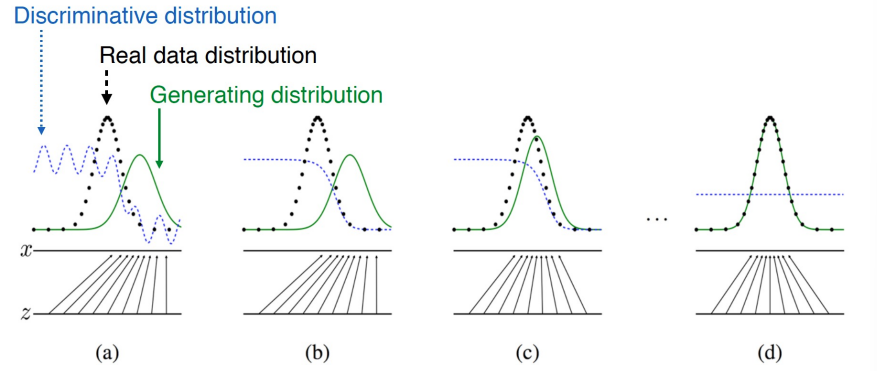

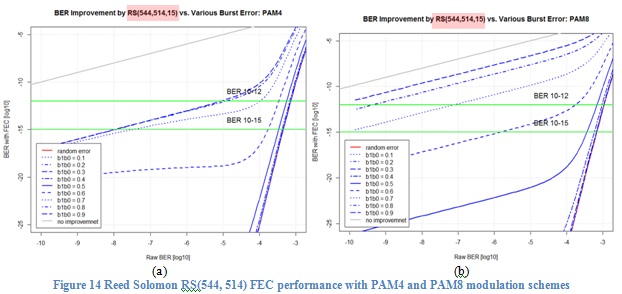

FEC 是下一代均衡技术的重要组成部分。我们的研究 [8] 表明,FEC 的性能(即通常以 10 的幂为单位的 BER 改进量)取决于多种因素,包括 FEC 方案、接收端的残余噪声、调制方案(例如 NRZ、PAM4、PAM8)、编码方案(例如线性编码、格雷编码)、均衡方案和设置。图 14 显示了 PAM4 和 PAM8 调制方案之间 Reed Solomon RS(544, 514, 10) FEC BER 增益的比较。

从图 14 可以看出,FEC BER 增益从 PAM4 到 PAM8 逐渐下降。原因在于,在 NRZ 方案中,只有两个电平,因此当噪声出现在外部区域时,错误不会进一步扩展。在 PAM4 或 PAM8 方案中,由于很可能紧邻另一个符号电平,因此出现在符号电平两端的噪声将继续增加错误概率。另一个关键因素是 ISI 和 DFE 抽头系数引起的突发错误。当噪声导致判决错误时,DFE 的反馈机制将经历较长的错误周期。判决错误的概率会随着 DFE 抽头系数的增加而增加。FEC 特性表明需要限制 DFE 系数。这意味着设计人员需要仔细平衡均衡方案,以保持解决方案空间。此外,如果 DFE 的功能由于 FEC 问题而受到限制,则意味着系统开发人员需要仔细控制系统中不相关噪声(例如串扰)的数量。

结论和后续步骤

本文回顾了各种通道均衡方案,并阐述了每种均衡方案在性能、功耗和面积 (PPA) 效率方面的优缺点。随着数据速率的提高和半导体工艺的进步,均衡方案的选择也将随之变化。我们还解释并比较了基于模拟的均衡架构(大多数低于 56Gbps 的收发器都采用这种架构)和基于 ADC 的收发器设计(我们认为后者将成为 112Gbps 及以上收发器的主流设计方法)。随着工艺节点的进步,过去阻碍基于 ADC 设计的功耗和面积问题变得更容易接受,同时使得能够使用 DSP 方法实现更复杂的均衡方案。

我们还进行了一系列实验,以检验均衡方案(尤其是 CTLE、FFE、DFE 和 FEC)的有效性。我们得出结论:虽然 DFE 能够以相对较短的抽头长度降低信道符号间干扰 (ISI),但 FFE 需要补偿前体符号间干扰 (ISI)、弥补 CTLE 的不足以及补偿收发器的 PVT 变化。此外,FFE 在均衡能力方面表现出更高的可扩展性,并且在 DSP 领域相对易于实现。我们还定量证明了 DFE 在处理串扰等不相关噪声方面的有效性。当使用 CTLE 和 FFE 等线性均衡器充分补偿信道符号间干扰 (ISI) 时,相对较短长度的 DFE 可以帮助系统改善 SNDR 和 BER。

我们还讨论了 FEC 及其与均衡方案的相互作用。我们的研究表明,为了提升 FEC 性能,系统开发人员和设备设计人员需要仔细平衡均衡方案并选择链路组件。

展望未来,下一代串行链路仍有许多未解决的领域和挑战。例如,基于ADC的收发器设计的延迟会大幅增加,这对于某些应用来说将是一个问题。随着未来对更高数据速率的需求不断增长,对PAM4和PAM8以外先进调制方案的探索将再次兴起。

参考

[1] ITRS 高速 I/O 速度路线图(2013 年修订版),ITRS,2013 年。

[2] J. Kurzweil,《数字通信导论》,纽约,John Wiley & Sons,2000 年。

[3] J. Proakis,《数字通信》,第四版,纽约,麦格劳希尔,2001 年。

[4] M. Li,《高速抖动、噪声和信号完整性》,Prentice Hall,ISBN 0132429616,2007年。

[5] “理解 Stratix IV GX 器件的预加重和线性均衡特性”,应用笔记 AP-602,Altera 公司,2010 年。

[6] J. Liu 和 X. Lin,“高速通信系统中的均衡”,IEEE 电路与系统杂志,2004 年 4-17 页。

[7] G. Clark 和 B. Cain,《数字通信的纠错编码》。Plenum Press,1981 年。

[8] M. Shimanouchi、H. Wu 和 M. Li,“用于高速串行链路 BER 仿真的行为 FEC 模型”,DesignCon 2018,加利福尼亚州圣克拉拉。

[9] MP Li和M. Shimanouchi,“高速链路抖动和BER的新型混合仿真方法”,DesignCon 2011。

[10] M. Li、M. Shimanouchi 和 H. Wu,“高速链路建模与仿真的进展”,CICC 2013。

[11] H. Wu、M. Shimanouchi 和 M. Li,“满足低 BER 要求的超长数据模式的高速链路仿真策略”,DesignCon 2014,加利福尼亚州圣克拉拉。