偶分频

//240个时钟周期翻转一次输出,这实际上是一个 480倍分频器

reg [7:0] counter= 0;

reg divided_clk = 1'b0;

always @(posedge clk) beginif (counter == 239) begin // 240counter <= 0;divided_clk <= ~divided_clk; end else begincounter <= counter + 1'b1;end

end

奇分频

- 对于任何奇数N分频,以将N(例如N为5)分解成两个部分:一部分用于决定高电平持续时间(2),另一部分用于决定低电平持续时间(3)。

5分频

假设要实现的是5分频。每五个输入时钟周期,输出信号就会有一个完整的周期,其中包含两个输入时钟周期的高电平和三个输入时钟周期的低电平,形成近似50%的占空比。

- 输出逻辑:

- 当计数器值小于2(即0或1),输出高电平;

- 当计数器值大于等于2(即2, 3, 或4),输出低电平。

- 即:

- 高电平持续时间为2个输入时钟周期

- 低电平持续时间为3个输入时钟周期

- 所以,占空比为:

占空比 = 2 2 + 3 = 40 % \text{占空比} = \frac{2}{2+3} = 40\% 占空比=2+32=40%

Verilog代码示例

module TEST (clk, rst, clk_out);input clk, rst;output reg clk_out;localparam HIGH_TIME = 2; reg [3:0] count;always @(posedge clk or posedge rst) beginif(rst)count <= 0;else if(count == 4)count <= 0;elsecount <= count + 1;endalways @(posedge clk or posedge rst) beginif(rst)clk_out <= 0;else if(count < 2)// 高电平时长clk_out <= 1;elseclk_out <= 0;end

endmodule

奇分频 占空比50%

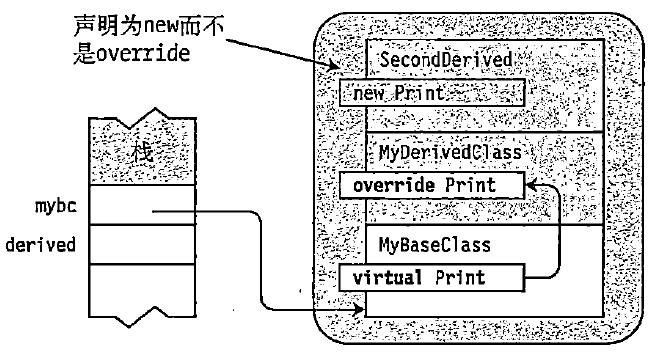

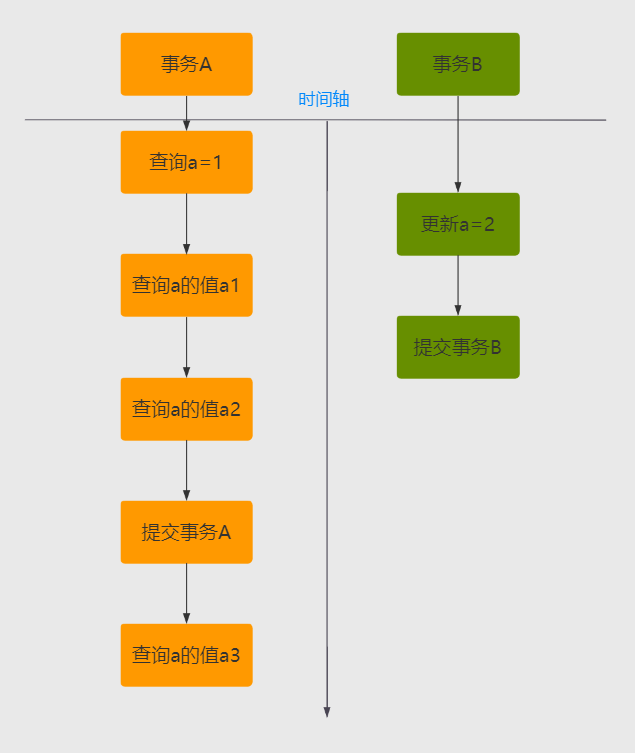

- 两个占空比非50%的n分频时钟相或运算,得到占空比为50%的奇数n分频时钟。

module nocdc (input clk,input rst,output divided_clk

);reg [2:0] counter = 0;

reg clk1, clk2;always @(posedge clk or posedge rst) beginif (rst) begincounter <= 0;clk1 <= 0;clk2 <= 0;end else begincounter <= counter + 1;// 第一个信号:前3个周期高if (counter < 3)clk1 <= 1'b1;elseclk1 <= 1'b0;// 第二个信号:后2个周期高,延迟2个周期启动if (counter >= 2 && counter < 5)clk2 <= 1'b1;elseclk2 <= 1'b0;end

endassign divided_clk = clk1 | clk2;endmodule

- 其他:双沿触发 + 计数器控制上升/下降沿

![[Windows] 剪映 视频编辑处理](https://i-blog.csdnimg.cn/direct/a237a0c2cd4c43469a55a71733737ea6.png)